日本テキサス・インスツルメンツ株式会社により出願された特許

11 - 20 / 219

エナジーハーベスタ・バッテリ充電回路及び方法

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

マルチステージシステムにおける増幅器オフセット及びノイズ低減

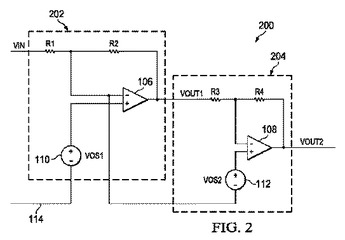

マルチステージ増幅器システム(200)が、一層良好な整合構成要素及び/又はトリム回路の必要性を低減する、ノイズ及びオフセット寄与を提供する。入力(VIN)を受け取り、出力(VOUT1)を供給する第1の増幅器(106)を有する第1の増幅器ステージ(202)が、第1のオフセット電圧(VOS1)を第1の増幅器ステージに提供し、供給レール(114)に結合される、第1のオフセット電源(110)を含む。出力(VOUT1)を入力として受け取り、出力(VOUT2)を提供する第2の増幅器(108)を有する第2の増幅器ステージ(204)が、第2のオフセット電圧(VOS2)を第2の増幅器ステージに提供する第2のオフセット電源(112)を含む。第2のオフセット電源は、第1のオフセット電圧からのノイズ寄与を低減するように第1の増幅器ステージに結合される。  (もっと読む)

(もっと読む)

半導体集積回路

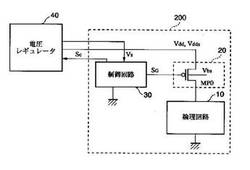

【課題】 ゲート酸化膜の信頼性を維持しながら、待機時のリーク電流を抑制でき、回路面積の増加を最小限にでき、欠陥を確実に検出することができる半導体集積回路を実現する。

【解決手段】 論理回路10と電源電圧Vddの供給端子との間にスイッチング回路20を設ける。動作時に、スイッチング回路20のトランジスタMP0のゲートに0Vの電圧を印加し、チャネル領域に電源電圧Vddと同じかまたは僅かに低いバイアス電圧VBを印加することで、トランジスタMP0のしきい値電圧を低くし、その電流駆動能力を大きくする。待機時にトランジスタMP0のゲートに電源電圧Vddと同じ電圧を印加し、ソースに電源電圧より低い電圧を印可し、チャネル領域に電源電圧Vddと同じかまたはそれより高いバルクバイアス電圧VBを印加し、トランジスタMP0のドレイン電流を最少化することにより、論理回路10の電流経路を遮断し、リーク電流の発生を抑制する。

(もっと読む)

エナジーハーベスタ回路のためのバッテリ保護回路及び方法

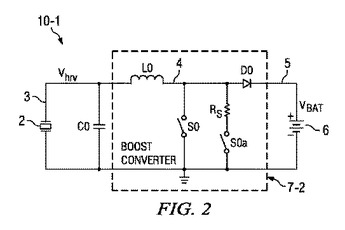

収集された電圧(Vhrv)をバッテリ(6)に印加される出力電圧(VBAT)に変換するための電力管理回路(7−2、3、4)であって、収集された電圧(Vhrv)を受け取るよう結合される第1の端子(3)と第1のスイッチ(S0)の第1の端子に結合される第2の端子とを有するインダクタ(L0)を含む。この電力管理回路は、バッテリ(6)がフル充電されていない場合、エナジーハーベスタ(2)により生成された電流をバッテリに転送し、フル充電されている場合、過充電を避けるため、その電流をバッテリ(6)からシャントする。  (もっと読む)

(もっと読む)

100BASE−Tイーサネットのためのフォールトトレラントモード

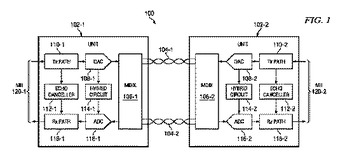

100BASE−T接続を維持するためイーサネットケーブル内で残っており大きくダメージを受けていないツイストペアの利用を可能とするシステムが、費用のかかる修繕及び障害なしに提供される。説明される装置は、送信経路(110)に結合されるデジタル・アナログ・コンバータ(DAC108)及び受信経路(118)に結合されるアナログ・デジタル・コンバータ(ADC116)を含む。媒体依存インタフェース(MDIX106)が、DAC及びADCに結合され、100BASE−Tイーサネット接続での通信のため第1のツイストペア(104−1)及び第2のツイストペア(104−2)を受信するよう適合される。ツイストペアフォールトが検出されると、MDIXがフォールトトレランスモードに入り、フォールトのないアクティブツイストペアで物理的全二重100BASE−Tリンクがつくられる。  (もっと読む)

(もっと読む)

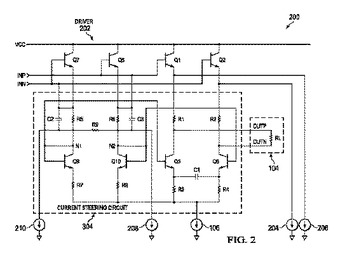

正確な電流ステアリングを備えた低電力高速差動ドライバ

BiCMOSプロセストランジスタを用いる混合又はハイブリッドモードドライバが、ドライバのプルアップ部の電圧に調和するプルダウン電流を生成するため電流ステアリング回路(電圧駆動差動対の代わりに)を有する。ドライバは、速度を速め、生成する出力同相電圧ゆらぎが一層小さい。回路200が、出力端子(OUTP、OUTN)を介して電流を供給して負荷104を駆動するドライバ202(これは、電圧モードと電流モードの組み合わせを用いる)を有する。ドライバ202は、NPNトランジスタ(Q1、Q2、Q7、Q8)、電流源(106、204、206)、及び電流ステアリング回路304を有する。電流ステアリング回路304は、フィードフォワード・レジスタ・キャパシタ(RC)ネットワーク(R5、R6、C2、C3)、入力NPNトランジスタ(Q9、Q10)、出力NPNトランジスタ(Q5、Q6)、電流源(208、210)、レジスタ(Rl〜R4及びR7〜R8)、及びバイパスキャパシタC1を有する。NPNトランジスタはPNPトランジスタで置き換えてもよい。  (もっと読む)

(もっと読む)

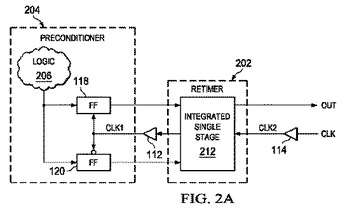

クロック分周器のための効率的なリタイマー

従来のリタイマーは全般的に、非常に多くの電力を消費し、ノイズが多く、大きすぎる。また、位相ノイズ及びジッタが、一般的にリタイミングの関数である。開示される装置において、電力消費が低減され、ノイズ特性が改善された、一層小さなフットプリントを提供するために、クロック分周器のためのリタイマー202のインテグレーテッド信号ステージ212と共に動作するようマッピングされるロジック206をプリコンディショナー204が有する。  (もっと読む)

(もっと読む)

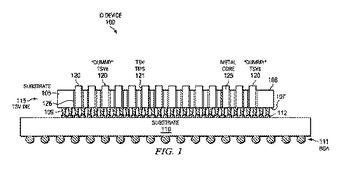

ICデバイスのエンハンストされた熱放散のための突出するTSV

集積回路デバイス(100)が、基板パッド(102)を含む上面を有する基板(110)、及び能動回路を含む上部半導体表面(107)と(底面)106とを含む半導体基板(105)を含む複数の基板貫通ビア(115)ダイを含む。上部半導体表面(107)は、基板の上面上の基板パッドに結合されるボンドコネクタ109を含む。複数の基板貫通ビア(TSV)が、底面から外に延びる突出するTSVティップ(121)に上側半導体表面から延びる内部金属コア(125)を含む。複数のTSVの少なくとも1つが、そこへの如何なる電気的接続もない、突出するTSVティップを有し、TSVダイの底面からの熱消散を可能にするための付加的な表面領域を提供するダミーTSV(120)である。

(もっと読む)

(もっと読む)

BiCMOSプロセス技術における高電圧SCRMOS

集積回路が、ドレイン領域(1010)及びSCR端子(1012)の周りに、低減された表面フィールド(RESURF)領域(1024)と共に形成されるSCRMOSトランジスタを含む。RESURF領域は、ドリフト領域(1014)と同じ導電型であり、ドリフト領域(1014)より一層重くドープされる。  (もっと読む)

(もっと読む)

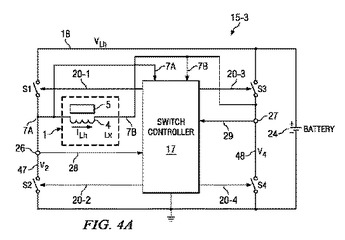

誘導エナジーハーベスタのための電力管理DC−DCコンバータ及び方法

コイルの第1(7A)と第2(7B)の端子間に結合されるスイッチング回路(S1〜S4)を含む、コイル(4)を含むハーベスティングデバイス(1)から収集されるACエネルギーを管理するためのシステム。スイッチング回路は、第1(S1)、第2(S2)、第3(S3)、及び第4(S4)のスイッチを含む。スイッチ・コントローラ(17)が、第2及び第4のスイッチを閉じてコイル内の電流(ILh)の増大を可能にし、第2及び第4のスイッチの一方を開き、増大されたインダクタ電流が所定のしきい値(Ihrv)に達するのに応答して第3及び第1のスイッチのうちの対応する1つを閉じて、増大されたインダクタ電流を、第3及び第1のスイッチのうちの対応する1つを通じて電流受信デバイス(24及び/又はRL、CL)へ導く。  (もっと読む)

(もっと読む)

11 - 20 / 219

[ Back to top ]