アオイ電子株式会社により出願された特許

31 - 40 / 85

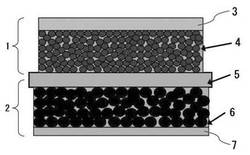

リチウム二次電池

【課題】高温時に放電可能とするとともに、電池容器破損時匂いを発散して電池容器に不具合があることを警告できるリチウム二次電池の提供。

【解決手段】正極、セパレータ、負極および電解質層からなるリチウム二次電池であって、該電解質層が、電池破損時に芳香させることが可能となる香料成分のエステル化合物を含有すること、より好ましくは、前記エステル化合物が、大気圧下、140℃以上の沸点を有する化合物であるリチウム二次電池。

(もっと読む)

パーティクル除去方法、微小ピンセット装置、原子間力顕微鏡および荷電粒子ビーム装置

【課題】微小ピンセットに付着したパーティクルが試料に再付着するのを防止する。

【解決手段】開閉自在な一対のアームを有するナノピンセット1を試料表面に近接させ、該試料表面に付着したパーティクルPを把持し、パーティクルPを把持したナノピンセット1を粘着部材3上まで移動し、パーティクルPを粘着部材3に接触させ、その後、ナノピンセット1を開いた状態で粘着部材3から遠ざけることにより、パーティクル除去を確実に行うことができる。

(もっと読む)

半導体装置

【課題】めっきを施さなくても外部電極の端面に半田フィレットを安定して形成できる半導体装置を提供する。

【解決手段】2点鎖線26に沿って、樹脂封止体25における金属板23の剥離面にV字の溝を形成する。V字型の溝の形成には、刃先がV字型であるブレード27を使用する。次に、切断用ブレード28を使用して、樹脂封止体25を2点鎖線26に沿って切断する。そして、一つの樹脂封止体25が分割され、半導体装置1が完成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】外部電極が設けられた面と反対側の面に受光面を備えており、小型化が可能である半導体装置を提供する。

【解決手段】ガラス基板41上に内部電極4Aとダミー電極44とを形成する。光検出半導体素子2Aをガラス基板41の内部電極4A上にフリップチップ接続する。ワイヤ7Aのループ高さを半導体素子2Aより高くなるように内部電極4Aとダミー電極44との間をワイヤボンディングする。樹脂封止した後、樹脂封止体62の上面を研磨して、ワイヤ7Aを内部電極4Aに接続したワイヤ7Aと、ダミー電極44に接続したワイヤ64とに分割する。ワイヤ7Aとを接続する外部電極を研磨面65に形成する。樹脂封止体62を分割する。その際、ダミー電極44とワイヤ64とを、光検出半導体装置1Aから切り離す。

(もっと読む)

半導体装置

【課題】リードをめっき処理する工程やリードを曲げる工程などにおけるクラックの発生を防止する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1Aは、リードフレーム3A,4Aに搭載した半導体素子2Aを樹脂6Aで封止したものである。半導体素子2Aは、リードフレームのダイパッド4Aにダイボンディングされ、リードフレームのリード3Aとワイヤ5Aでワイヤボンディングされる。半導体装置1Aの底面11Aには、ダイパッド4Aの底面(半導体素子2Aがダイボンディングされていない面)全体が露出している。露出しているダイパッド4Aの周囲には、半導体素子2Aを封止している樹脂6Aからなる額縁状の凸部61Aが形成されている。凸部61Aとダイパッド4Aの外周端41Aとは所定長だけ離れている。

(もっと読む)

微小試料台、その作成方法、微小試料台集合体、および試料ホルダ

【課題】試料ホルダを運搬中に微小試料片Sの破損を回避すること。

【解決手段】微小試料台10は、全てシリコン製であり、基部11、固定部12及びガード部13を有する。微小試料片Sは、固定部12の頂部に立てて固定される。微小試料台10は、基部11の上面11Aに2本の固定部12と3本のガード部13が交互に突設された一体化構造である。ガード部13の厚さは固定部12よりも厚く、ガード部13の高さ(Z方向の長さ)は固定部12よりも高く作製する。

(もっと読む)

サーマルヘッド駆動用集積回路

【課題】複数のシフトレジスタを有し、シフトレジスタ内に余りビットをなくするようにしたサーマルヘッド駆動用集積回路を提供する。

【解決手段】データ信号を順次転送して格納する複数のシフトレジスタSR1〜SR3のシフトレジスタSR1に一個のデータ信号入力端子を、シフトレジスタSR3に一個のデータ信号出力端子が設けられている。サーマルヘッドの発熱体ドット数に対応するビット数をシフトレジスタの総ビット数から選択する選択回路14の選択信号Sa、Sbの組み合わせに応じて複数のシフトレジスタを切り替える切り替え手段19を備える。シフトレジスタにデータ信号が入力されて外部に出力される際、シフトレジスタからの出力ビット数が変わってもシフトレジスタ内に余りビットが発生せず、また、データ信号入力端子とデータ信号出力端子を共通にすることができ、集積回路にデータ信号出力端子を追加して設ける必要がない。

(もっと読む)

ナノピンセットおよびその製造方法

【課題】汚れにくいナノピンセットの提供。

【解決手段】ナノピンセット1は、開閉自在な一対のアーム3と、アーム3の各々に形成された試料把持部3aと、各アーム3の少なくとも試料把持部3aを含む領域に形成された撥水性膜とを備えることを特徴とする。撥水性膜には、例えば、導電性を有する撥水性膜や化学吸着単分子膜が用いられる。

(もっと読む)

半導体装置

【課題】半導体素子のチップサイズを小さくすることなく小型化することができる半導体装置を提供する。

【解決手段】略矩形形状の半導体素子2の端子2bとワイヤ5で接続する外部電極3bを略矩形形状の半導体装置1の隅に設けた。そして、半導体装置1の辺1aと半導体素子2の辺2aとのなす角度が45°になるように半導体素子2を傾けて配置した。

(もっと読む)

回路構成情報生成装置、制御装置、回路検証システム、回路検証方法、回路構成情報生成プログラム及び制御プログラム

【課題】プログラマブル素子を用いて被検証回路の動作検証を行う場合に、コンパイルを再度行うことなく、また、コンパイル後の回路構成情報を直接的に変更することなく、プログラマブル素子から出力する被検証回路の内部信号を変更可能な回路検証システム、回路検証方法、回路構成情報生成装置、制御装置、回路構成情報生成プログラム及び制御プログラムを提供する。

【解決手段】被検証回路の回路構成が記載されたRTLソースファイルと、観測信号名及び出力ビット位置が記された観測信号設定ファイルとを取得し、指定された内部信号を被検証回路の最上位階層の回路ブロックから出力し、MUX0〜MUX127及び制御レジスタ110を追加して、複数の観測信号からいくつかを選択して出力する回路構成の検証用RTLソースファイルを生成する。この回路をFPGAに構成し、制御レジスタ110のレジスタ値を更新して、出力する信号を変更する。

(もっと読む)

31 - 40 / 85

[ Back to top ]