エルピーダメモリ株式会社により出願された特許

101 - 110 / 2,599

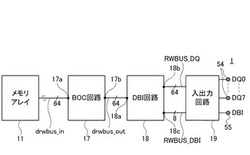

半導体装置

【課題】BOC回路を削減することで、回路面積の縮小及び消費電力の低減を実現する。

【解決手段】半導体装置1は、複数の第1のデータ線dwbus_inと、複数の第2のデータ線dwbus−outと、複数の第3のデータ線RWBUS_DQと、複数の第4のデータ線RWBUS_DBIと、アドレス情報に従って複数の第1のデータ線dwbus_inから供給された複数のリードデータの順序を並べ替えて複数の第2のデータ線dwbus−outへ供給するBOC回路17と、所定の条件に従って、複数の第2のデータ線dwbus−outから供給されたリードデータを反転して複数の第3のデータ線RWBUS_DQへ供給するDBI回路18と、を備える。好ましくは、DBI回路18は、反転の情報を示す判定ビットを生成して複数の第4のデータ線RWBUS_DBIへ供給する。

(もっと読む)

論理回路及びデータ処理システム

【課題】素子数が少なく、遅延が小さく、ドライバ能力を有するXORゲート回路を提供する。

【解決手段】論理回路1は、電源電位VPERIとノードn1の間に接続されたトランジスタT1と、電源電位VPERIとノードn2の間に接続されたトランジスタT2と、電源電位VSSとノードn3の間に接続されたトランジスタT3と、電源電位VSSとノードn4の間に接続されたトランジスタT4と、ノードn1とノードn3の間に直列接続されたトランジスタT5,T7と、ノードn1とノードn3の間に直列接続されたトランジスタT9,T11と、ノードn2とノードn4の間に直列接続されたトランジスタT6,T8と、ノードn2とノードn4の間に直列接続されたトランジスタT10,T12とを備える。出力信号Yは、トランジスタT5,T7の接続点及びトランジスタT6,T8の接続点から取り出される。

(もっと読む)

半導体装置

【課題】動作速度と駆動能力とのバランスが調整された多入力論理回路を備えた半導体装置を提供する。

【解決手段】3入力以上の入力端子を含み当該3入力以上の入力端子の論理レベルについて論理演算を行う多入力論理回路(XOR_H)を備え、当該多入力論理回路は、それぞれ2つの入力端子を含み当該2つの入力端子の論理レベルに対して前記論理演算を行う複数の2入力論理回路を含み、当該複数の2入力論理回路は、第1の2入力論理回路(XOR_D61)と当該第1の2入力論理回路よりも占有面積が小さく駆動能力が小さい第2の2入力論理回路(XOR_F61、XOR_F62)とを含み、前記第1の2入力論理回路が前記多入力論理回路の最終段として動作し、前記第2の2入力論理回路が前記第1の2入力論理回路に信号を供給する前段回路の少なくとも一部として動作することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】チップ積層体を構成する半導体チップのクラックを防止しつつ、半導体装置のコストアップを抑制する手段を提供する。

【解決手段】半導体装置1はチップ積層体11と絶縁材料から成る補強層16を有する。チップ積層体11は、貫通電極13を有する複数の半導体チップ10が互いに積層されて成る。補強層16は、チップ積層体11の一方の端に位置する第1の半導体チップ10の、チップ積層体11の他の半導体チップとは反対側の一面に形成されている。

(もっと読む)

半導体装置

【課題】入力信号に基づいて位相の一致した相補の出力信号を生成する。

【解決手段】半導体装置に含まれるスプリッター回路10は、入力信号INTを受けて反転信号IB1を出力するインバータINV1と、反転信号IB1を受けて非反転信号IT1(第1の出力信号)を出力するインバータINV2が縦続接続される信号パスPASS1を含む。また、スプリッター回路10は、入力信号INTを受けて反転信号IB3(第2の出力信号)を出力するインバータINV3を含む信号パスPASS2を含む。また、インバータINV3と補助インバータINVCは出力信号線を共有する。インバータINV3と補助インバータINVCは、共に、入力信号INTの反転信号を電源とする。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置のトランジスタのシリコンピラー上部に活性領域を設ける際に、エピタキシャル成長により前記シリコンピラー上部に形成されるシリコン膜の高さが、前記トランジスタ毎にばらつくことを防ぎ、前記シリコン膜への導電型ドーパントの注入深さを均一にする半導体装置の製造方法を提供する。

【解決手段】基板の主面に柱状のシリコンピラーを形成するシリコンピラー形成工程と、前記シリコンピラーを覆うように第1の絶縁膜を形成する第1絶縁膜形成工程と、前記第1の絶縁膜を上面から除去し、前記シリコンピラー上部の上面及び側面を露出させる第1絶縁膜除去工程と、前記シリコンピラー上部の上面及び側面にエピタキシャル成長法によりシリコン膜を形成するシリコン膜形成工程とを有する。

(もっと読む)

半導体装置

【課題】テスト回路をリセットするテスト信号発生回路を備えた半導体装置を提供する。

【解決手段】活性レベルのテストモード信号に基づきテストを実行するテスト回路(CKT1〜CKT4)と、テストモード設定コマンドに基づいて活性レベルのテストモード信号(TMS)を出力するテスト信号発生回路(106)と、外部から入力される半導体装置の動作を有効とする有効信号(CKE)に基づいて前記テスト信号発生回路が前記テストモード信号を電源投入時から所定期間非活性レベルに維持させるリセット回路(40)と、を備える

(もっと読む)

半導体装置及びデータ処理システム

【課題】外部電圧VDDの変動に伴うレイテンシカウンタのラッチマージンの低下を抑制する。

【解決手段】半導体装置10は、外部電圧VDDで動作する第1の回路と、外部電圧VDDよりも低い内部電圧VPERIで動作する第2の回路とを有するデータ入出力回路78と、外部クロック信号CK,/CKに基づき、データ入出力回路78の動作タイミングを制御する内部クロック信号LCLKOETを生成するDLL回路23とを備え、DLL回路23は、内部電圧VPERIで動作する回路を含む一方、外部電圧VDDで動作する回路を含まないことを特徴とする。

(もっと読む)

半導体装置

【課題】素子分離すべき領域にダミーの補助ゲートを配置することで、電気的に分離する方法(FS方式)を採用しつつ、補助ゲートに給電するための新たな専用の配線を設けることによるチップの縮小化の弊害を解消する半導体装置を提供する。

【解決手段】半導体基板2に埋め込み形成された素子分離膜によって、複数のセル部活性領域が区画された半導体装置1であって、半導体基板2に設けられたゲート溝内に、ゲート絶縁膜を介して形成された補助セルゲート28aが、半導体基板2と電気的に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】複数の埋め込みゲート型トランジスタが形成されたメモリセル領域と周辺回路領域を有する半導体装置の製造において、前記埋め込みゲート型トランジスタの半導体層とコンタクトプラグとの接触抵抗及び前記埋め込みゲート型トランジスタ毎の電流駆動特性のばらつきの増加を防ぐ。

【解決手段】半導体基板上に第1の半導体層と、前記第1の半導体層の下面と接する前記第1の半導体層よりも低い不純物濃度である第2の半導体層とを形成する工程と、前記第1の半導体層及び前記第2の半導体層から成る活性領域を少なくとも2つの領域に分ける溝内にゲート絶縁膜を介してゲート電極を形成する工程と、前記半導体基板の主面を覆う層間絶縁膜を形成する工程と、前記層間絶縁膜を貫通して前記第1の半導体層の上面の一部を露出させるコンタクトホールに導電膜を埋め込んでコンタクトプラグを形成する工程を有する半導体装置の製造方法。

(もっと読む)

101 - 110 / 2,599

[ Back to top ]