エルピーダメモリ株式会社により出願された特許

11 - 20 / 2,599

半導体装置

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

半導体装置及びその製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

半導体装置の製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

半導体装置及びその製造方法

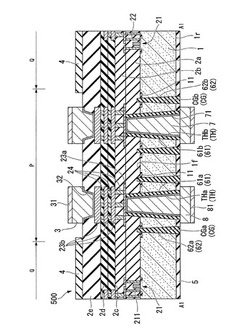

【課題】貫通電極に、加工性と機能性の双方を高めた絶縁リングを設ける。

【解決手段】ドライエッチングにより形成された絶縁リング用環状溝CGa,CGbには絶縁物質が充填され、単独絶縁リング62a,62bが形成されている。また、ドライエッチングにより形成されたTSV用貫通孔THa,THbの側壁は、絶縁膜で覆われ、TSV側壁絶縁リング61a,61bが形成されている。また、TSV用貫通孔THa,THbの残りの部分には、シード/バリア層71を介して、例えば銅のような誘電体が充填されており、それによりTSV7が形成されている。TSV側壁絶縁リング61の厚さは、絶縁リング用環状溝CGの幅、言い換えれば、単独絶縁リング62の厚さの約半分である。従って、TSV側壁絶縁リング61の厚さは、TSV側壁絶縁リングを単独で設けた場合のその厚さの3分の1程度にすることができる。

(もっと読む)

半導体装置の製造方法

【課題】オーバーハング部を持つ2段以上の積層構造であっても、オーバーハング部の支持を確実にできる半導体装置の製造方法を提供する。

【解決手段】複数の第1電極パッド11が配置された第1半導体チップ10を配線基板50上に搭載する工程と、複数の第2電極パッド21が配置された第2半導体チップ20を、第1半導体チップの短辺に対し第2半導体チップの短辺が直角に位置し、配線基板と第2半導体チップの短辺との間に隙間を形成するべく、第1半導体チップ上に積層する工程と、隙間に、第2半導体チップの長辺側から第2半導体チップの短辺と平行な方向に向かって第1アンダーフィル23を充填する工程と、第1電極パッドと配線基板に形成された接続パッド51とを第1ワイヤ61で電気的に接続する工程と、第1アンダーフィルを充填する工程後、第2電極パッドと接続パッドとを第2ワイヤ61で電気的に接続する工程と、を含む半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】ワード線の選択回路のサイズを縮小することにより、半導体装置のサイズを縮小する。

【解決手段】メインワード線は、複数のグループに分類され、メインワードドライバはアドレス情報にしたがってメインワード線を選択する。4本のメインワード線MWL0〜MWL3から構成される1つのグループが、1つのレベルシフタ118を共有する。アドレス情報は、グループ選択のための第1アドレスとメインワード線選択のための第2アドレスを含む。メインワードドライバは、第1アドレスにしたがって、第1グループ選択回路や第2グループ選択回路128aを選択し、選択された第2グループ選択回路128aのレベルシフタ118は活性電位(ローレベル)を出力する。そして、選択された第2グループ選択回路128aに所属する複数のメインワード線MWL0〜MWL3のうちの1本が第2アドレスA3,A4により選択される。

(もっと読む)

メモリモジュール

【課題】Load Reduced型のメモリモジュールにおいてメモリデバイスの搭載位置によるデータのスキューを低減する。

【解決手段】データコネクタを有するモジュール基板110と、複数のメモリデバイス201〜236と、データコネクタとメモリデバイスとの間に接続されたデータレジスタバッファ301〜309とを備える。モジュール基板110は、メモリデバイスが搭載されたメモリ搭載領域A1,A2と、平面視でメモリ搭載領域A1,A2に挟まれた位置に定義され、データレジスタバッファが搭載されたレジスタ搭載領域Bとを有する。各メモリデバイスとデータレジスタバッファとの配線距離がほぼ均一になるため、メモリデバイスの搭載位置によるデータのスキューが低減される。

(もっと読む)

半導体チップ及びその抵抗測定方法、並びに半導体装置

【課題】本発明は、貫通電極のサイズ(直径)が縮小化された場合でも、4端子法により貫通電極の抵抗値を正確に測定することの可能な半導体チップ及びその抵抗測定方法、並びに半導体装置を提供することを課題とする。

【解決手段】半導体基板101及び回路素子層102を有する半導体チップ本体55と、半導体チップ本体55を貫通する第1乃至第4の貫通電極61〜64と、回路素子層102に設けられた回路素子を介することなく、第1の貫通電極61と第2の貫通電極62とを電気的に接続する第1の導電経路96と、回路素子を介することなく、第1の貫通電極61と第3の貫通電極63とを電気的に接続する第2の導電経路97と、回路素子を介することなく、第2の貫通電極62と第4の貫通電極64とを電気的に接続する第3の導電経路98と、を有する。

(もっと読む)

半導体装置

【課題】半導体装置の動作テストのスループットを向上させる。

【解決手段】判定回路112は、2つのメモリバンクBANK(A)、BANK(E)から読み出される計16ビットのテストデータを検査する。検査対象となる16ビットのメモリセルMCにはすべて「H」の書き込みが実行されており、いずれのメモリセルMCに異常がなければそのまま「H」が読み出される。判定回路112は、メモリバンクBANK(A)のテストデータ同士を比較する第1検出回路124とメモリバンクBANK(E)のテストデータ同士を比較する第2検出回路126に加えて、更に、メモリバンクBANK(A)のテストデータとメモリバンクBANK(E)のテストデータを比較する第3検出回路128を備える。

(もっと読む)

メモリモジュール

【課題】Registered型のメモリモジュールにおいてメモリチップに供給するコマンドアドレス信号の信号品質を向上させる。

【解決手段】コマンドアドレス信号CAが供給されるコマンドアドレスコネクタ121を有するモジュール基板510と、メモリデバイス201〜272と、コマンドアドレスレジスタバッファ401,402とを備える。コマンドアドレスレジスタバッファ401は、メモリデバイス201〜236にコマンドアドレス信号CAを供給し、コマンドアドレスレジスタバッファ402は、メモリデバイス237〜272にコマンドアドレス信号CAを供給する。本発明によれば、複数のコマンドアドレスレジスタバッファを用いていることから、メモリチップの数が多い場合であってもモジュール基板上における配線負荷が低減され、その結果、メモリチップに供給するコマンドアドレス信号の信号品質が向上する。

(もっと読む)

11 - 20 / 2,599

[ Back to top ]