エルピーダメモリ株式会社により出願された特許

21 - 30 / 2,599

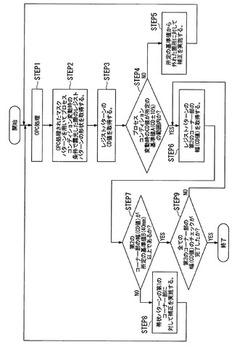

マスク作成方法、及び半導体装置の製造方法

【課題】デフォーカス時において、レジストパターンのコーナー部での断線の抑制が可能であり、マスク作成工程におけるプロセスマージンを拡大する。

【解決手段】第1のコーナー部を有する帯状パターンを含むマスクパターンの設計レイアウトデータに対してOPC処理を行う工程STEP1と、OPC処理されたマスクパターンを用いて、プロセスコンディション変動時の条件で露光した際のレジストパターンの形状を取得する工程STEP2と、第1のコーナー部に対応するレジストパターンの第2のコーナー部の幅を取得する工程STEP6と、第2のコーナー部の幅が所定の基準値以下である場合、透光性基板に形成された帯状パターンの第1のコーナー部の内側に補正パターンを配置する工程STEP8と、を有する。

(もっと読む)

半導体装置

【課題】異なる配線を介して異なる電源端子から内部回路を構成する第1の回路および第2の回路にそれぞれ給電する際に、第1の回路に給電する配線と第2の回路に給電する配線との間に発生するノイズを抑制する。

【解決手段】半導体装置は、第1の回路に給電を行う第1の電源配線と、第2の回路に給電を行う第2の電源配線と、第1の電源配線と第2の電源配線との間に容量素子を設けることにより、両端子間のインピーダンスを、大幅に低減させることにより異種電源間のノイズを低減する。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタとコンタクトパッド間のコンタクト抵抗の上昇を防ぎ、書き込み・読み出し不良を低減する、装置特性が優れた半導体装置を提供する。

【解決手段】タングステン膜8bを形成する工程と、タングステン膜8b上に窒化チタン膜からなる下部電極13を形成する工程と、酸化雰囲気下で窒化チタン膜に熱処理を行うことにより窒化チタン膜を酸化する工程と、下部電極13上に容量絶縁膜14を形成する工程と、容量絶縁膜14上に上部電極15を形成する工程と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】微細化に対応した半導体装置を提供する。

【解決手段】半導体基板の第1の領域内に第1の方向に沿って交互に配置されるように第1及び第2の素子分離領域を形成する。この際、第1及び第2の素子分離領域のうち少なくとも一方の素子分離領域の側面は半導体基板の主面に対して垂直とならないように第1及び第2の素子分離領域を形成する。この後、第1及び第2の素子分離領域の上部を除去して、第1の素子分離領域と第2の素子分離領域の間の半導体基板をフィンとして形成する。

(もっと読む)

半導体チップ及び半導体装置

【課題】本発明は、半導体チップを構成する第1及び第2のバンプ電極の頂部の位置のバラツキを抑制することで、第1のバンプ電極と他の基板(例えば、半導体チップや配線基板)とをフリップチップ接合した際の電気的接続信頼性を向上させることの可能な半導体チップ及び半導体装置を提供することを課題とする。

【解決手段】基板35と、基板35の一面35aに配置された電極パッド36と、電極パッド36を露出するように、基板35の一面35aに設けられた絶縁膜37と、電極パッド36上に設けられた第1のバンプ電極41と、絶縁膜37上に設けられた第2のバンプ電極42と、を有し、第2のバンプ電極42が第1のバンプ電極41よりも小さい径で構成されている。

(もっと読む)

半導体装置

【課題】容量を充放電させ信号を遅延させる回路の遅延時間の温度依存性を緩和し回路規模の増大を抑制可能とした半導体装置の提供。

【解決手段】互いに異なる電源電圧を与える第1の電源(VDD)と第2の電源(VSS)の間に直列に接続され、制御電極が共通に接続された第1及び第2のFET(M11、M12)と、前記第1及び第2のFETの間に接続する第1の回路を有するインバータを備え、前記第1の回路は、互いに並列に接続された第1の抵抗素子(R12)と第3のFET(M13)を備え、前記第1の抵抗素子(R12)の抵抗値は正の温度特性を有し、前記第3のFET(M13)は、その動作範囲に、第3のFET(M13)の端子間抵抗が、第1の抵抗素子(R12)の温度特性と逆極性の負の温度特性を示す領域を含む。

(もっと読む)

半導体装置およびその検査方法

【課題】ウエハ検査時に必要なプローブピンを削減可能にした半導体装置を提供する。

【解決手段】第1のデータを記憶する記憶素子と、データ読み出しの指示が入力されると、記憶素子から第1のデータを読み出して出力するデータ入出力制御部と、データ入出力制御部から出力される第1のデータを第1の端子に出力し、第1のデータを第1の端子に出力するとき、自装置の第2の端子と他の半導体装置の第1の端子とを接続するプローブカードを介して他の半導体装置から受信する第2のデータを保持し、その後、第2のデータを自装置の第1の端子に出力するデータラッチ部とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】下層の銅配線と上層のアルミニウム配線とを接続するコンタクトプラグのコンタクト抵抗を均一化する。

【解決手段】銅配線8と、銅配線9上の層間絶縁膜10と、層間絶縁膜10上に形成されたアルミニウム配線17と、銅配線9とアルミニウム配線17とを電気的に接続するプラグ13とを備える半導体装置であって、プラグ13は銅とアルミニウムの合金からなり、銅配線9上のコンタクトホールにバリアメタルを設けずに第1のアルミニウム膜を充填し、熱処理して合金化し、未反応の第1のアルミニウム膜を除去した後、アルミニウム配線用の第2のアルミニウム膜を成膜する。

(もっと読む)

半導体装置及びその製造方法

【課題】所望の領域に容易に第1の膜を形成して半導体装置の不良を低減する。また、スループットが向上して、製造コストの低減を図る。

【解決手段】半導体装置の製造方法では、半導体基板の第1及び第2の領域上に第1の膜を形成した後、第1の膜上にフォトレジストパターンを形成する。フォトレジストパターンをマスクに用いた第1の膜のエッチングにより、第2の領域上の第1の膜を除去すると共に第2の領域上を覆うように被覆膜を形成する。半導体基板に熱処理を行うことにより、被覆膜を除去すると共にフォトレジストパターンに焼き締め処理を行う。この後、フォトレジストパターンを除去する。

(もっと読む)

半導体ウェハ、半導体装置及びその製造方法

【課題】アライメントマークに集中する応力の方向依存性を低減して、クラックを発生しにくくする。

【解決手段】基板の第1の主面に、環状の第1の溝及びドット形状の第2の溝を形成する。第1及び第2の溝を埋め込むように絶縁膜を形成した後、基板の第1の主面にフォトレジスト膜を形成する。絶縁膜で埋め込まれた第2の溝の基板上での位置を基準として位置合わせした第1のパターンを、フォトレジスト膜に転写する。絶縁膜で埋め込まれた環状の第1の溝の内側に位置する基板に、基板を厚さ方向に貫通する貫通電極を形成する。

(もっと読む)

21 - 30 / 2,599

[ Back to top ]