エルピーダメモリ株式会社により出願された特許

41 - 50 / 2,599

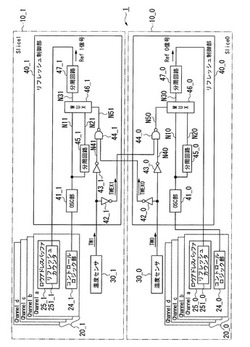

半導体装置

【課題】不要にリフレッシュ周期が変更されることによる無駄な消費電流を削減する。

【解決手段】複数の半導体チップを備え、複数の半導体チップのうちの第1の半導体チップは第1の温度センサを有し、第1の半導体チップとは異なる第2の半導体チップはリフレッシュ動作を必要とする半導体チップであって、第1の半導体チップの第1の温度センサの出力結果に応じて第2の半導体チップのリフレッシュ周期が変更される。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の断線による縦型トランジスタの故障を改善すること。

【解決手段】半導体装置は、第1の方向(Y)に互いに隙間を空けて形成された複数の半導体ピラー(5A1〜5A5)から成る半導体ピラー群(5)を含む。半導体ピラー群(5)の内、両端部を除く中間部に位置する半導体ピラー(5A2〜5A4)のいずれか1つである特定の半導体ピラー(5A3)と隣接して、ダミーピラー(6)が第1の方向(Y)と直交する第2の方向(X)に設けられている。ゲート絶縁膜(10)が、複数の半導体ピラー(5A1〜5A5)の各々の外周面とダミーピラー(6)の外周面の一部とに形成されている。ゲート絶縁膜(10)を介して、複数の半導体ピラー(5A1〜5A5)の間の隙間と特定の半導体ピラー(5A3)とダミーピラー(6)との間の隙間とを埋めるように、ゲート電極(11)が、複数の半導体ピラーの側面とダミーピラーの側面とに形成されている。

(もっと読む)

半導体ウェハ、半導体装置及びその製造方法

【課題】アライメントマーク終端部への応力集中により基板にクラックが発生することを軽減する。

【解決手段】基板の第1の主面に、第1の主面に対向して見た場合に、環状の第1の溝及び終端部を有さない形状の第2の溝を形成する。第1及び第2の溝を埋め込むように絶縁膜を形成した後、基板の第1の主面にフォトレジスト膜を形成する。絶縁膜で埋め込まれた第2の溝の基板上での位置を基準として位置合わせした第1のパターンを、フォトレジスト膜に転写する。絶縁膜で埋め込まれた環状の第1の溝の内側に位置する基板に、基板を厚さ方向に貫通する貫通電極を形成する。

(もっと読む)

半導体装置

【課題】ダミーマットの占有面積を縮小する。

【解決手段】半導体装置は、ビット線32と、ビット線に接続された複数のメモリセル31と、ダミービット線52と、ダミービット線にソース及びドレインの一方が接続された複数のダミーセルトランジスタ51と、ビット線とダミービット線との間に接続されたセンスアンプ33とを有し、複数のダミーセルトランジスタの各々のソース及びドレインの他方は、フローティング状態にされるか、又はダミービット線に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】エッチングによるマスク窒化膜除去時に、STI構造を構成しているライナー膜に劣化が発生することを防止する。

【解決手段】半導体基板に形成したトレンチ内に素子分離構造を形成する工程を含み、前記素子分離構造を形成する工程は、前記トレンチ内の前記半導体基板上にパッド酸化膜を形成する工程と、前記パッド酸化膜上にALD法によりライナー膜を形成する工程と、前記ライナー膜上にSOD膜を形成する工程と、を含む半導体装置の製造方法。ライナー膜は酸化ハフニウム膜が好ましい。

(もっと読む)

半導体装置、メモリカード、データ処理システムおよび半導体装置の製造方法

【課題】歩留まりや信頼性の低下を招くことなく、隣接セルのフローティング・ゲート間の結合容量を小さくすることができ、隣接セルの書き込み情報の影響を小さくした状態でフローティング・ゲートの電位を制御することが可能なNAND型フラッシュメモリを提供する。

【解決手段】一導電型の半導体材料層表面のチャネル領域上方に第2の絶縁膜12を介して形成されたゲート電極部と、ゲート電極部の上方に前記ゲート電極部と一体形成されたキャパシタ電極部と含むフローティング・ゲート13と、キャパシタ電極部の側面を囲むように第1の絶縁膜12を介して形成されたコントロールゲート10となる第1の電極と、を有する。

(もっと読む)

半導体装置

【課題】分割抵抗回路で消費される消費電力を低減することが可能な半導体装置を提供する。

【解決手段】半導体装置は、抵抗分割回路で抵抗分割された分割電圧を受けるための入力端子と、入力端子から供給される分割電圧と、所定の基準電圧と、の電圧差を検出する検出回路と、外部から入力信号を受けるための信号入力端子と、分割電圧と入力信号の電圧を比較するカレントミラー回路と、を備え、カレントミラー回路は、検出回路が検出した電位差に応じて、カレントミラー回路に入力される分割電圧を実効的に補正する電位補正回路と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】個別の工程で形成されることで分離して配置された電極どうしを断線することなく接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、半導体基板の主面に第2の絶縁膜を介して形成された第2の電極との間に補償膜を埋設する。第1の電極及び第2の電極上には、第1の電極の上面及び第2の電極の上面と接触する、第1の電極の上面から補償膜の上面を経由して第2の電極の上面まで到達する配線を形成する。

(もっと読む)

半導体装置の製造方法

【課題】縦型トランジスタのソース又はドレイン用の拡散層を形成するにあたって形成されるシリコン膜に表面凹凸を発生させない半導体装置の製造方法を提供する。

【解決手段】複数の半導体ピラーを形成する工程と、隣り合う前記半導体ピラーで挟まれた溝の側面を覆うように絶縁膜を形成する工程と、前記絶縁膜の前記溝の底部に近い領域に側面開口を形成する工程と、前記溝の内部を覆うようにシリコン膜からなる被覆膜を形成する工程と、前記被覆膜上に前記半導体ピラー内へ拡散させる不純物で構成された不純物層を形成する工程と、前記不純物を、前記側面開口を塞ぐように形成されている前記被覆膜を通して前記半導体ピラー内に熱拡散させてソース又はドレイン用の拡散層を形成する工程と、を含む。前記被覆膜の成膜温度を510℃より高く度550℃未満の範囲とすることにより、非晶質状態のシリコン膜を形成する。

(もっと読む)

半導体装置

【課題】半導体装置の共通規格に依存してテストモードのリセットを行うのではなく、自律してテストモードのリセットを行う半導体装置が、望まれる。

【解決手段】半導体装置は、内部回路のテストを可能にする第1のテスト部と、第1のテスト部の動作状態を制御可能な第2のテスト部と、第2のテスト部が、第1のテスト部のリセット状態を解除したことに応答して活性化されると共に、第1のテスト部の活性化から所定の期間が経過後に、リセット信号を発生するテストリセット部と、を備えている。第2のテスト部は、テストリセット部が発生するリセット信号を受け付けた場合に、第1のテスト部をリセット状態とする。

(もっと読む)

41 - 50 / 2,599

[ Back to top ]