エルピーダメモリ株式会社により出願された特許

61 - 70 / 2,599

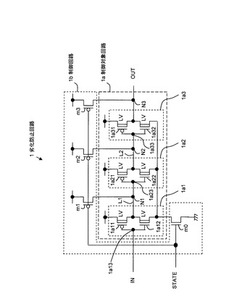

半導体装置

【課題】スタンバイ状態時における第1導電型のトランジスタでの劣化を抑制可能な半導体装置を提供する。

【解決手段】半導体装置は、第1導電型のトランジスタを含み縦列接続された複数の回路と、複数の回路の其々の入力端子のうち他の回路と接続された接続入力端子と接続し接続入力端子の電圧を制御するための制御信号の活性化に応じて、接続入力端子に、該接続入力端子から電圧を受け付ける回路内の第1導電型のトランジスタを非導通状態とする第1の電圧を供給する制御回路と、を備える。

(もっと読む)

半導体装置の製造方法、及び半導体製造装置

【課題】吸着ツールに対する半導体チップの位置ずれを補正して被搭載体に搭載可能となり、被搭載体に対する半導体チップの位置精度の向上が図れる半導体装置の製造方法、および、製造装置を提供する。

【解決手段】半導体チップ2を吸着ツール12で吸着する工程と、吸着ツールに吸着された半導体チップの裏面から赤外線カメラ13で赤外線画像を撮影することにより半導体チップの表面にあるアライメントマークの位置を検出する工程と、赤外線カメラによって検出されたアライメントマークの位置に基づいて吸着ツールに対する半導体チップの位置ズレを補正して半導体チップを被搭載体3に搭載する工程と、を含む。

(もっと読む)

半導体記憶装置及びそのテスト方法

【課題】ロールコールテストに要する工数を削減できる半導体記憶装置及びそのテスト方法を提供する。

【解決手段】不良アドレスが格納される不揮発性の記憶素子を備えた半導体記憶装置にロールコールテスト時にマスク用テストモード信号を出力するテスト制御回路とロールコール回路とを備える。ロールコール回路は、アドレス信号と不良アドレスとをビット単位で比較し、その比較結果を出力する。また、ロールコール回路は、マスク用テストモード信号が入力されると、アドレス信号の所望のビットに対応する比較結果をマスクして上記アドレス信号と不良アドレスとが一致していることを示す値を出力すると共に、マスクされていないビットに対するロールコールテストを可能にする。

(もっと読む)

情報処理システム、制御システム及び半導体装置

【課題】制御システムがメモリシステムのバンクグループにアクセスする際の効率を高めることが可能な情報処理システムを提供する。

【解決手段】本発明の情報処理システムは、例えば、メモリシステム20と、アクセス制御部15を含む制御システム13とを備えている。メモリシステム20は、記憶領域が複数のバンクにより構成され、この複数のバンクが複数のバンクグループにグループ化されている。アクセス制御部15は、複数のプロセシングエンジンによるアクセスの優先順位に対応し、バンクグループ毎にレイテンシを含むアクセス情報を第1のレジスタ15aに保持し、バスマスタ11aを介してプロセシングエンジンからのアクセス要求を受けたとき、第1のレジスタ15aを参照し、その内容に基づいてアクセス対象のバンクグループに対するアクセスをフレキシブルに制御する。

(もっと読む)

半導体装置

【課題】積層され、貫通電極で相互に接続された複数の半導体チップの出力インピーダンスのバラツキを抑える。

【解決手段】半導体装置100は、第1の被制御チップ110と、第1の被制御チップ110を制御する制御チップ120とを備える。第1の被制御チップ110は、第1の出力回路と同一の構成を持つ第1のレプリカ出力回路111と、第1のレプリカ出力回路111に接続される第1のZQ端子112と、第1のZQ端子に接続される第1の貫通電極113と、第1のレプリカ出力回路111のインピーダンスを設定する第1の制御回路114と、を含む。制御チップ120は、第1の貫通電極113に接続される第2のZQ端子121と、第2のZQ端子121の電圧と参照電圧Vrefとを比較する比較回路122と、比較回路122からの比較結果に応じて処理を行う第2の制御回路123と、を含む。

(もっと読む)

レイアウトデータ作成装置及び半導体装置

【課題】従来のようにピラーの分割単位が小数点数とならず、単位ピラートランジスタのピラーの径の変更を行う必要が無くなり、半導体装置を製造するプロセスを複雑化することなく、ピラー型のトランジスタによりセルを、セルロウ内に効率的に配置するレイアウトデータ作成装置を提供する。

【解決手段】本発明のレイアウトデータ作成装置は、集積回路における複数の単位ピラー型トランジスタで構成されるピラー型トランジスタを、配置領域内に配置可能な単位ピラー型トランジスタの整数単位に分割し、配置領域内に配置するサブピラー型トランジスタを生成するトランジスタ調整部2を備えている。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板をエッチングする際、ハードマスクの肩落ちによるエッチング深さの基板面内での粗密差を低減する。

【解決手段】半導体基板1上に、絶縁層(10,11)とアッシング除去可能な材料層を形成する工程と、材料層をパターニングする工程と、パターニングされた材料層をマスクに、絶縁層を貫通し、少なくとも半導体基板の一部をエッチングする第1のエッチング工程と、材料層がなくなる前にエッチングを一旦停止し、残存する材料層(12)をアッシング除去する工程と、絶縁層をマスクに半導体基板を所定の深さにエッチングする第2のエッチング工程とを含む。

(もっと読む)

ICソケット

【課題】被検査対象装置の反りや外部端子の寸法公差による接触不良を防止可能なICソケットを提供する。

【解決手段】ICソケット100は、半導体装置51の半田ボール67と接触するポゴピン3を複数備え、複数のポゴピン3は、半田ボール67と接触する上端面4がテーパ形状を有し、テーパ形状のテーパの向きが、隣接するポゴピン3同士で異なるものがある。

(もっと読む)

半導体装置およびその制御方法

【課題】テストモード時にテストモードがリセットされるのを防ぐ。

【解決手段】本発明の半導体装置1は、外部から入力されるコマンドに応じて、半導体装置を通常動作モードまたはテストモードで動作させるテスト制御回路220と、通常動作モード時または前記テストモードにおける所定期間外に所定のコマンドが入力されると、テストモードリセット信号TRSTを活性化してテスト制御回路220に入力し、テストモードにおける所定期間内は、所定のコマンドが入力されても、テストモードリセット信号TRSTを活性化しないテストモードリセット制御回路210と、を有する。

(もっと読む)

半導体装置

【課題】被制御チップの出力回路から制御チップの入力回路へ伝送されるデータ信号の位相を、入力回路に供給される同期信号の位相に一致させる。

【解決手段】半導体装置は、第1の被制御チップ110とそれと積層する制御チップ120を備える。第1の被制御チップは、同期信号に応じてデータ信号を出力する第1の回路117と、そのデータ信号を遅延同期信号に同期してデータ端子へ出力する入出力回路118と、出力回路を模した回路であって、遅延同期信号に同期してレプリカ信号を第1のレプリカ端子へ出力するレプリカ回路119とを含む。制御チップは、同期信号を出力し、データ信号を受ける第1の制御回路126と、同期信号を遅延させて遅延同期信号として出力する遅延調整回路130と、レプリカ信号の位相と同期信号の位相とを比較する位相比較回路128と、位相比較回路の比較結果に基づいて遅延調整回路の遅延量を制御する遅延制御回路129とを含む。

(もっと読む)

61 - 70 / 2,599

[ Back to top ]