エルピーダメモリ株式会社により出願された特許

81 - 90 / 2,599

半導体装置及びこれを備える半導体モジュール

【課題】データ出力バッファの正確なインピーダンスキャリブレーション動作を行う。

【解決手段】電源ラインVL1とデータ端子24との間に接続されたP型トランジスタユニット201と、電源ラインVL1とキャリブレーション端子ZQとの間に接続されたP型トランジスタユニット111〜114と、キャリブレーション端子ZQの電位が基準電位VREFと一致するよう、P型トランジスタユニット111〜114インピーダンスを調整し、一致した状態におけるP型トランジスタユニット111〜114の一つのインピーダンスをP型トランジスタユニット201に反映させるインピーダンス制御回路とを備える。これにより、基準電位VREFが電源電位VDDの半分のレベルからオフセットしたレベルに設定されている場合であっても、正確なキャリブレーション動作を行うことができる。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、シリコン層上に、抵抗値が低く、かつ平坦性の良好なニッケルモノシリサイド層を形成可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】基板に形成されたシリコン層を覆ように白金を含むニッケル層を堆積する工程であって、シリコン層に近い部分では遠い部分と比較して結晶性が低くなるように、白金を含むニッケル層を堆積する工程S05と、基板を加熱することで、シリコン層と白金を含むニッケル層との界面にニッケルモノシリサイド層を形成する工程S07と、を有する。

(もっと読む)

半導体装置

【課題】より少ない調整ステップでキャリブレーションを完了する。

【解決手段】出力端子(DQに相当)と、出力端子と接続され、出力端子を調整可能なインピーダンスで駆動する出力回路(210に相当)と、出力回路のインピーダンスを段階的に調整するキャリブレーション回路(100)と、を備え、キャリブレーション回路は、キャリブレーション動作の実行を指示するコマンドを受けて、インピーダンスの調整を開始し、インピーダンスを変化させる変化幅を、開始直後に対し以降においてより狭めるように調整する。

(もっと読む)

半導体装置及びその製造方法

【課題】柱状半導体層の幅を広く維持することができる半導体装置を提供すること。

【解決手段】半導体装置は、一つの直線上に順に形成された、第1、第2及び第3の柱状半導体層と、第2及び第3の柱状半導体層の間の空間であって第2及び第3の柱状半導体層の側面に夫々設けられた第1及び第2のゲート電極と、第1及び第2の柱状半導体層の間の空間及び第2及び第3の柱状半導体層の空間に埋め込まれた層間絶縁膜とを有する。層間絶縁膜は、第1及び第2の柱状半導体層の間の空間内であってゲート電極を介することなく第1及び第2の柱状半導体層の側面に形成され、第2及び第3の柱状半導体層の間の空間内であって第1及び第2のゲート電極を介して第2及び第3の柱状半導体層の側面に形成されている。

(もっと読む)

半導体装置

【課題】半導体チップに構成されるメモリコアにおける電源系を容易に分離可能な配線構造を実現しスループットの向上が可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体チップC1に複数のメモリコア(DRAMコア)が構成される。各メモリコアは、第1電源によって動作しパラレルデータを双方向に伝送するデータバスを駆動する第1回路領域と、第1電源と分離された第2電源によって動作しデータバスを伝送されるパラレルデータと外部端子を介して入出力されるシリアルデータとを双方向に変換する第2回路領域と含む。第1貫通電極群23は、第1回路領域に第1電源を供給する複数の貫通電極をY方向に並べて配置され、第2貫通電極群21は、第2回路領域に第2電源を供給する複数の貫通電極をY方向と交差するX方向に並べて配置される、それぞれの貫通電極群を経由して第1及び第2電源の配線群が互いに分離した配置で形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極膜に注入したイオンがチャネル領域に達してMISFETの電気特性に影響を与えていた。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

(もっと読む)

半導体装置

【課題】ストローブ信号の変化によって基準電位に重畳するノイズを低減し、これにより、基準電位を用いる入力レシーバ回路の動作マージンの低下を防止する。

【解決手段】ストローブ信号IDQSTによって活性化され、入力信号DQの電位と基準電位VREFとを比較することによって出力信号IDQRを生成する入力レシーバ回路17Rと、ストローブ信号IDQSTの変化によって基準電位VREFに生じるノイズをキャンセルするノイズキャンセラ100Tとを備える。本発明によれば、ノイズキャンセラ100Tによって基準電位VREFに生じるノイズがキャンセルされることから、入力レシーバ回路17Rの動作マージンを十分に確保することができる。これにより、高速なデータ転送を行うことが可能となる。

(もっと読む)

半導体装置

【課題】パリティエラーが発生した場合に適切な処理を実行する。

【解決手段】例えば、アクセスすべきメモリセルMCのアドレスを示すアドレス信号ADD及びアクセスの種別を示すコマンド信号CMDを外部から受け、これらに基づいてメモリセルアレイ11にアクセスするアクセス制御回路20を備える。アクセス制御回路20は、外部から供給される検証信号PRTYに基づいてアドレス信号ADD及びコマンド信号CMDを検証する検証回路90を含む。検証回路90は、アドレス信号ADD又はコマンド信号CMDがエラーであると判定した場合、メモリセルアレイ11へのアクセスを停止する。これにより、いわゆるパリティエラーなどの不良が検出された場合、誤ったコマンドの実行によってデータが破壊されたり、誤ったアドレスにデータを上書きしたりすることがない。

(もっと読む)

半導体装置およびその製造方法

【課題】電流―電圧特性の向上およびオン電流を増大することが可能で、高速動作に優れた半導体装置及びその製造方法を提供する。

【解決手段】半導体基板12の主面に形成され、第1の方向に延在する複数の活性領域と、活性領域を区画する素子分離領域と、半導体基板12の主面に形成されたものであって、平面視して複数の活性領域に交差する方向に延在する複数のゲート溝と、ゲート溝のそれぞれに埋め込まれた複数のゲート電極22と、を備えた半導体装置であって、ゲート溝のそれぞれの底面には、第1の方向に延在すると共に、上面71aが半導体基板12の主面よりも低い位置に配置する一対の突起部71が形成されており、ゲート電極22は、ゲート絶縁膜21を介して突起部71の上面71aと内側面71bと外側面71cとを覆ってなる、ことを特徴とする。

(もっと読む)

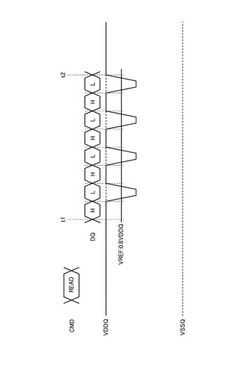

半導体装置

【課題】相補の信号によりプルアップバッファ回路とプルダウンバッファ回路を制御し、レベルシフタ関連回路をコンパクトに構成する。

【解決手段】半導体装置10は、プルアップバッファ回路100とプルダウンバッファ回路200を排他的にオン・オフ制御することによりデータ端子DQからデータを出力する。シリアライザ300は、相補な内部データ信号DT1/DC1を出力する。レベルシフタ370は、内部データ信号DT1/DC1の電圧レベルを変換し、相補な内部データ信号DT2/DC2を同時生成する。プルアップバッファ回路100とプルダウンバッファ回路200は、この変換後の内部データ信号DT2/DC2により制御される。

(もっと読む)

81 - 90 / 2,599

[ Back to top ]