インテグレイテッド・デバイス・テクノロジー・インコーポレイテッドにより出願された特許

1 - 1 / 1

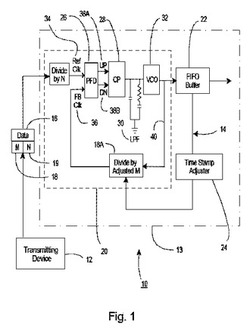

受信側デバイスの出力クロック周波数の補正回路

データ(16)およびタイムスタンプ要素(18)を受信する受信側デバイス(13)の出力クロックの周波数を補正するための出力クロック補正回路(14)は、出力クロックフィードバックループ(20)、FIFOバッファ(22)およびタイムスタンプアジャスタ(24)を含む。出力クロックフィードバックループ(20)は、タイムスタンプ要素(18)に基づいて出力クロックの位相および/または周波数を調節する。FIFOバッファ(22)は、一時的にデータを格納する。タイムスタンプアジャスタ(24)は、FIFOバッファの状態に基づいてタイムスタンプ要素を選択的に調節する。一実施形態では、前記状態が、FIFOバッファ内の実データレベルに少なくとも部分的に基づくものとなる。別の実施形態では、FIFOバッファ(22)が目標データレベル範囲を有し、FIFOバッファ内の実データレベルがこの範囲外となったときに、タイムスタンプ要素が調節される。 (もっと読む)

1 - 1 / 1

[ Back to top ]