アンバーウェーブ システムズ コーポレイションにより出願された特許

1 - 8 / 8

画定された不純物勾配を有するひずみ材料層を使用する半導体構造、およびその構造を製作するための方法。

【課題】不純物の無い区域を有するひずみ材料層を含む半導体構造とデバイス、及びそれを製作するための方法を提供する。

【解決手段】ひずみ材料層104の特定の領域108は、半導体の隣接する部分から相互拡散することができる不純物を無い状態にしておく。不純物がひずみ材料層104の特定の領域108に存在する場合、デバイス性能の低下となる。説明された特徴を有する、又は説明されたステップに従って製作される半導体構造100とデバイス(例えば、電界効果トランジスタ、即ち「FET」)を使用することにより、デバイスの動作が向上する。

(もっと読む)

代替活性エリア材料の集積回路への組み込みのための解決策

結晶半導体基板上に代替材料のエリアを形成する方法、並びにこの方法により形成された構造。このような代替材料のエリアは、MOSFET又は電子デバイス若しくは光電子デバイスにおける活性エリアとしての使用に適している。  (もっと読む)

(もっと読む)

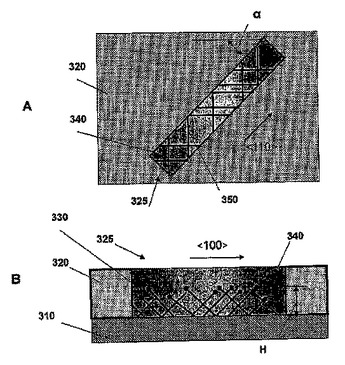

転位欠陥密度の低い格子不整合半導体構造およびこれに関連するデバイス製造方法

貫通転位が実質的にない上部分を有する制限されたエリア領域を備えている、モノリシック格子不整合半導体ヘテロ構造の製造、ならびにこのような格子不整合ヘテロ構造をベースとした半導体デバイスの製造。  (もっと読む)

(もっと読む)

高品質の緩和シリコンゲルマニウム層の製造方法

半導体材料上のSi1−xGex層の堆積中、パーティクル生成を最小限化する方法が、Si前駆体と、分解温度がゲルマンより高いGe前駆体とを含む雰囲気中に基板を設けるステップ、および最終Ge含有量が約0.15より大きくかつパーティクル密度が約0.3パーティクル/cm2より小さいSi1−xGex層を前記基板上に堆積するステップを含む。 (もっと読む)

シャロートレンチアイソレーションプロセス

トランジスタとトレンチ構造とを含む構造に関し、トレンチ構造は、トランジスタのチャネル領域内に歪みの一部のみを導入する。  (もっと読む)

(もっと読む)

構造均一性を有する半導体構造

組成変動を有する半導体層を備えている半導体構造を形成する。この半導体層の最上表面は、実質的にヘイズを有していない。  (もっと読む)

(もっと読む)

CMOSプロセス中に歪み半導基板層を保護する方法

Si/SiGeヘテロ構造をベースとしたウェハで不都合な表面材料の多量の消費を回避する酸化方法を、様々な中間CMOS熱酸化ステップに代えて行う。まず、酸化物堆積法を利用して、表面シリコンをほとんどまたは全く消費することなく、任意の厚さの酸化物を形成する。このような酸化物、例えばスクリーン酸化物およびパッド酸化物は、表面層との反応および表面層の消費によってではなく、表面層への堆積によって形成される。別の態様では、酸化物の堆積は、短時間の熱酸化ステップ、例えば急速熱酸化によって行われる。この場合、熱酸化が短時間であるために、表面Siはほとんど消費されず、Si/酸化物境界面は高い品質を有する。次に、堆積によって、この酸化物の厚みを所望の最終厚さにまで増大させる。さらに、この薄い熱酸化物層は、バリヤ層として働くことができ、これにより、後続の酸化物堆積と関連する汚染を防ぐことができる。  (もっと読む)

(もっと読む)

半導体デバイス製造のためのゲート材料

電子デバイスを形成する際、半導体層を予めドープして、ドーパント分布アニールをゲート画定前に行う。場合によっては、ゲートは金属から形成されている。したがって、続いて形成される浅いソースおよびドレインは、ゲートアニールステップの影響を受けない。  (もっと読む)

(もっと読む)

1 - 8 / 8

[ Back to top ]