ケイデンス デザイン システムズ,インコーポレイテッドにより出願された特許

1 - 2 / 2

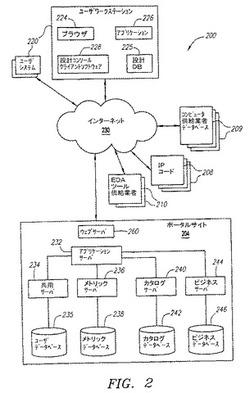

遠隔に位置するリソースを用いてチップ設計を行う方法およびシステム

【課題】遠隔に位置するリソースを用いてチップ設計を行う方法およびシステムを提供すること。

【解決手段】多面的な設計プラットフォーム(104)は、チップ上の複雑なコアベースシステムを設計するフロントエンドハードウェアIC設計者に対するツールとして動作する。設計プラットフォーム(104)は、ネットワークを利用して、既に設計された仮想コアブロックへのアクセスをサーチし、達成する。設計プラットフォーム(104)は、選択された仮想コアブロックについての全ての関連情報を選択(306)かつ転送(308)する手段を提供して、設計者がすぐに仮想コアブロックを新たなSoC設計へ組み込めるようにする。設計プラットフォーム(104)はさらに、複数の公知の検証ツールによる即時の利用のために、適切な安全なコアファイル(320)を生成して、仮想コアブロックおよび基本のSoC設計の機能の統合および接続の両方を検証する。

(もっと読む)

製造を理解した設計および設計を理解した製造

本発明のいくつかの実施態様は、集積回路(「IC」)レイアウトを設計するための製造を理解したプロセスを提供する。このプロセスは、ICレイアウトに基づいてICを製造するために使用される一組の機械に対して一組の製造設定を指定する製造構成を受ける。このプロセスは、この指定された製造構成に基づいて一組のデザインルールを規定する。このプロセスは、このICレイアウトを設計するためにこの一組のデザインルールを使用する。本発明のいくつかの実施態様は、集積回路(「IC」)を製造するための設計を理解したプロセスを提供する。このプロセスは、関連した一組の設計プロパティを備えたIC設計を受ける。このプロセスは、ICを製造するために使用される一組の機械に対して一組の製造設定を指定する製造構成を指定し、ここでこの指定された一組の製造設定は、この一組の設計プロパティに基づく。このプロセスは、製造設定に基づいてICを製造するものである。 (もっと読む)

1 - 2 / 2

[ Back to top ]