アナログ ディヴァイスィズ インクにより出願された特許

1 - 10 / 23

レールツーレールDMOS増幅器の出力ステージにバイアスをかけるための方法及び装置

【課題】レールツーレールDMOS増幅器の出力ステージにバイアスをかけるための方法及び装置を提供する。

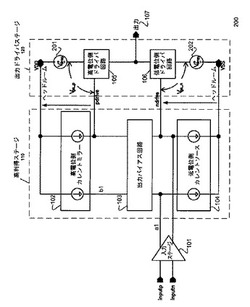

【解決手段】本願発明は、増幅器であって、入力信号を受け取るための入力ステージと、前記入力ステージに連結されると共に、前記入力信号に応答して出力ドライバステージに対して駆動信号を提供する高利得ステージと、前記出力ドライバステージに連結された出力端子とを具備することを特徴とする。前記出力ドライバステージは、前記高利得ステージから第1の駆動信号“pdrive”を受け取る第1の端子、第1の電圧降下を通じてVDDに連結された第2の端子、及び、前記増幅器の前記出力端子に連結された第3の端子を有する高電位側ドライバ回路を備える。

(もっと読む)

垂直集積システム

【課題】コストのかかる空間をとらずに電子部品内に個別パッシブ部品を組み込むことが可能な垂直集積システムを提供する。

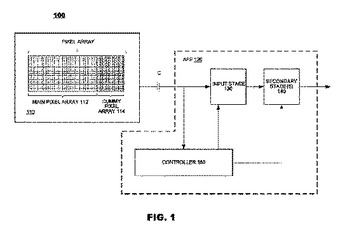

【解決手段】集積回路システム100は、半導体ダイ110の前面上に製造された第一のアクティブ層と、半導体ダイ110の裏面上の第二の予め製造された層とを含み、その第二の予め製造された層は、その中に埋め込まれた電気部品を有し、その電子部品は、少なくとも一つの個別パッシブ部品140を含む。また、集積システム100は、第一のアクティブ層及び第二の予め製造された層を結合する少なくとも一つの電気経路150も含む。

(もっと読む)

電気容量を測定するためのシステム及び方法

駆動回路の出力ピンに接続された負荷回路の電気容量を検査するためのシステム及び方法が提供される。一実施例において、前記方法は、前記出力ピンにおける電圧を第1の電圧まで駆動する段階と、所定の電流を前記出力ピンに印加する段階と、前記出力ピンにおける電圧を基準電圧と比較する段階と、前記出力ピンにおける電圧が前記基準電圧に一致する場合に、定期的な電圧変化期間の開始点と、前記出力ピンにおける電圧が前記基準電圧に一致する時刻との間に発生するクロック周期の数に基づいて、前記出力ピンに存在する電気容量の推定値を生成する段階とを含む。  (もっと読む)

(もっと読む)

スイッチ損失を改善するための回路アーキテクチャを有するデジタル/アナログ変換器

【課題】従来の電圧モードDACよりも、線形性が改善され、スイッチエリアの全体が小さく、そして寄生電気抵抗に鈍感なデジタル/アナログ変換器(DAC)を提供する。

【解決手段】デジタル/アナログ変換器(DAC)は、それぞれハイ基準電圧またはロー基準電圧のそれぞれに結合された第1入力をそれぞれ有するオペアンプ対を具備する。前記DACは、複数のスイッチ制御されるセルを具備し、それぞれ、抵抗器および2つのフォース/センススイッチ対を具備する。それぞれのセル内において、4つの全てのスイッチは、抵抗器と結合されている。第1フォーススイッチは、第1オペアンプの出力と結合されるとともに、結合されているセンススイッチは、第1オペアンプの反転入力に結合されている。第2フォーススイッチは、第2オペアンプの出力に結合されるとともに、結合されているセンススイッチは、第2オペアンプの反転入力に結合されている。

(もっと読む)

ファロー構造に基づくコンテンツ適応スケーラ

本発明の実施形態は、画像処理システムを対象とする。画像処理システムは、入力ピクセルのシーケンスを受信するための入力を有し、入力ピクセルの隣接する対の間の検出された差異に基づいて調整可能パラメータを生成するように構成されたコンテンツ検出モジュールと、入力ピクセルのシーケンスのための入力およびコンテンツ検出モジュールの出力に結合された制御入力を有するデジタルフィルタとを備えることができる。デジタルフィルタは、パラメータによってフィルタリング係数を調整できる。  (もっと読む)

(もっと読む)

低電力基準電圧およびバイアス電流発生器のための方法および回路

低電力で動作可能であり、プロセスばらつきの影響を受けにくく、占有するシリコン面積が少なく、ノイズが少ない、抵抗器無しのPTATセルを得るためのシステムおよび方法が提供される。さらに、カスケード接続のユニットセルによって基準電圧および基準電流を一定比率で増大させるためのシステムおよび方法が提供される。さらに、PTAT構成要素が微調整されるシステムおよび方法が提供され、有利なことにプロセスばらつきが少なくなり、温度の影響を受けにくくなる。  (もっと読む)

(もっと読む)

アパーチャ遅延不整合によって発生する時間インタリーブのアナログ−デジタル変換器内の誤差を減少させる方法

時間インタリーブADCシステム内でアパーチャ遅延をランダム化するためのシステムは、前記システム内の各ADCに対応する複数の選択スイッチ・ステージと、電圧源に接続した第2選択スイッチ・ステージとを具備する。複数の導線が、前記システム内のADCの数を超えて、前記第2選択スイッチ・ステージと前記選択スイッチ・ステージの各々との間に延びている。前記システム内のN個のADCの各々に対して、前記選択スイッチ・ステージおよび前記第2選択スイッチ・ステージは、前記ADCの前記サンプリング・キャパシタの各々から前記電圧源まで延びる少なくともN+1個の選択可能な導電性パスを有する。前記N+1個のパスのランダム選択は、アパーチャ遅延をランダム化できる。  (もっと読む)

(もっと読む)

分離されたNMOSベースのESDクランプセルのためのシステムおよび方法

本発明は、ICチップをESDから保護するための保護回路に関する。集積回路チップのためのESD保護回路は、分離されたNMOSトランジスタを備えていて、これは、バックゲートを基板から分離している分離領域と、バックゲート上に形成された第1および第2ドーピング領域およびゲートとを有している。ESD保護回路は、分離領域を第1電気ノードに接続する第1端子と、第2ドーピング領域を第2電気ノードに接続する第2端子とを更に備え得る。第1電気ノードは、第2電気ノードより高い電圧レベルを有していてもよく、かつゲートおよびバックゲートは、第2端子に接続され得る。  (もっと読む)

(もっと読む)

画像フロントエンド用のスイッチ式キャパシタ入力段

本発明の実施形態は、DC復元動作を制御するアナログフロントエンド(AFE)増幅器用の装置および制御方法を提供する。例示的な方法によると、AFEの第1の入力段が、高入力インピーダンスを有し、画像センサ画像アレイの第1の所定の領域における入力漏れ電流をほぼ引き出さない、連続時間増幅として動作するように制御される。第1の入力段は、画像センサ画像アレイの第2の所定の領域におけるDC復元機能を有するサンプルホールド増幅器として動作するように制御される。一実施形態によると、AFE入力段は、センサの作動状態画像アレイからの画素を読み出すとき、連続時間増幅として動作するが、いわゆる「黒レベル」画素に対応する画像アレイからの画素、または別途センサの作動状態画像フィールドの外部にある画素を読み出すときは、DC復元を有するサンプルホールド増幅器として動作する。  (もっと読む)

(もっと読む)

マルチチャンネル画像システムにおける不一致を低減するためのディザリング技術

本発明の実施形態は、マルチチャンネル画像システムに向けられる。マルチチャンネル画像システムは、光信号のための入力と複数のチャンネル回路とを含むことができる。各チャンネル回路は、光信号のいくつかの部分をデジタル表示に変換するアナログ信号処理チェーンを有することができ、複数のチャンネル回路は、同時に動作することができる。マルチチャンネル画像システムはまた、ディザを追加するために、少なくとも1つのアナログ信号処理チェーンの点に接続される少なくとも1つのディザ回路を具備することができる。  (もっと読む)

(もっと読む)

1 - 10 / 23

[ Back to top ]