マイクロン テクノロジー インコーポレイテッドにより出願された特許

1 - 5 / 5

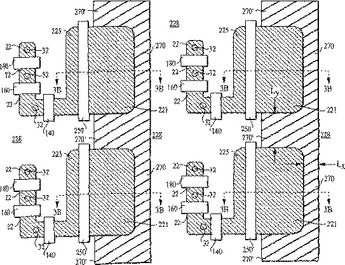

CMOSイメージセンサにおける暗電流を減少させる接地ゲート及び分離技術

半導体装置の領域を分離する分離方法及び装置を提供する。分離装置及び方法では、電界分離領域上に且つイメージセンサのピクセルに隣接させて、バイアスされるゲートを形成する。分離方法では更に、電界分離領域の大部分の上に分離ゲートを形成して、ピクセルアレイのピクセルを互いに分離する。分離方法及び装置では更に、能動領域内に分離溝を形成し、この分離溝に、シリコンを含有しドーピングされた導電性材料を充填する。基板の能動領域内に溝を設け、この溝内にエピタキシャル層を成長させてこの溝を完全に充填するか、又は部分的に充填して、エピタキシャル層上及び溝内に絶縁材料を堆積して溝を完全に充填することにより、領域を互いに分離する方法及び装置をも提供する。  (もっと読む)

(もっと読む)

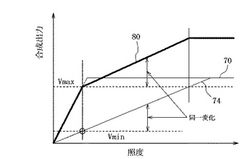

選択読取りによる広ダイナミックレンジ撮像デバイス

【課題】ダイサイズおよびI/Oピンの数を増大することなく増大したダイナミックレンジを有するイメージャおよび該イメージャの動作方法を提供することにある。

【解決手段】デュアル積分、選択読取り動作方法を用いるワイドダイナミックレンジイメージャであり、一つの読取りチェーンを必要とするのみである。一画素行からの第1の信号を第1の積分期間後にディジタル化しメモリに記憶する。第1の積分期間中に所定の閾値に到達した各画素に対してフラグをセットしメモリに記憶する。同一の画素行からの第2の信号を第2の短い積分期間後に読み取る。画素の対応するフラグビットがセットされた場合には、第2の信号を記憶し(第1の信号に上書きする)、続いて処理回路で使用してフルレンジ信号と第2の信号の組み合わせに基づく適切な画素信号を生成する。そうでない場合には、第1の信号を処理回路で処理する。

(もっと読む)

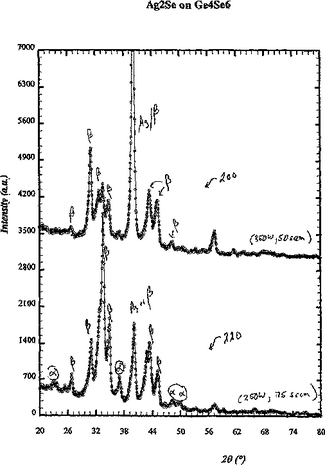

スパッタ堆積におけるセレン化銀膜の化学量論及び形態の制御

セレン化銀のスパッタ堆積方法、及びスパッタ堆積されたセレン化銀膜の化学量論、ノジュール型欠陥の生成及び結晶構造の制御方法。該方法は、約0.3mTorr〜約10mTorrの圧力でのスパッタ堆積プロセスを用いて、セレン化銀を堆積させることを含む。本発明の一視点によれば、RFスパッタ堆積プロセスを、好ましくは、約2mTorr〜約3mTorrの圧力で用いることができる。本発明のもう一つの視点によれば、パルスDCスパッタ堆積プロセスを、好ましくは、約4mTorr〜約5mTorrの圧力で用いることができる。本発明のもう一つの視点によれば、アルファセレン化銀とベータセレン化銀の両方を含むセレン化銀膜を、約10mTorrの圧力及び約250W未満のスパッタ電力の下でスパッタ堆積させることができる。  (もっと読む)

(もっと読む)

共有結合粒子を有する研磨パッドおよび研磨パッドの製造方法

【課題】研磨中に研磨パッドからの研磨粒子の離脱に起因するスクラッチの発生がない半導体ウエハの化学的−機械的研磨用研磨パッドを提供する。

【解決手段】研磨パッド10は、本体11、分子結合リンク30、および本体全体に実質的に均一に分散した研磨粒子20を有する。本体11はポリマー性マトリクス材料12から作製され、分子結合リンク30はマトリクス材料12に共有結合される。実質的に全ての研磨粒子20は、少なくとも1つの分子結合リンク30に共有結合される。分子結合リンク30は、研磨粒子20をマトリクス材料12に確実に固定し、パッド全体への研磨粒子20の分布の均一性を増強し、実質的に研磨粒子20がパッドから脱離するのを防止する。

(もっと読む)

フリップチップ用高性能シリコンコンタクト

本発明においては、前面(14)と背面(16)とを備える半導体基板(12)であって、基板を(12)通って前面(14)と背面(16)との間を延びる孔(18、20、22)を備える半導体基板(12)を用意する。孔(18、20、22)は、部分的に、内壁部分によって規定され、外側導電性シースを形成する。導電性材料(54)を、内壁部分の少なくとも一部に隣接して形成する。その後に誘電体材料層(56)を、孔内部に、導電性材料上であってそのラジアル方向内側に形成する。次に第2の導電性材料(60)を、孔内部に、誘電体材料層(56)上であってそのラジアル方向内側に形成する。後者の導電性材料は、内側導電性コアキシャル線要素を構成する。 (もっと読む)

1 - 5 / 5

[ Back to top ]