株式会社ルネサステクノロジにより出願された特許

91 - 100 / 4,790

半導体装置の製造方法

【課題】デュアルメタルゲート構造を有する半導体装置において、ゲート電極除去する工程において、ゲート絶縁膜に与える損傷を抑える。

【解決手段】 第1のトランジスタと第2のトランジスタとを備える半導体装置において、第1のトランジスタは、第1の仕事関数を有する第1の材料からなる第1のゲート電極と、第1のゲート絶縁膜とを含む。また、第2のトランジスタは、第2の仕事関数を有する第2の材料からなる第2のゲート電極と、第2のゲート絶縁膜とを含む。ここで、第1のゲート絶縁膜は、高誘電率膜と、第1の高誘電率膜上に形成された第1の絶縁膜とを含むものとする。第2のゲート絶縁膜においては、高誘電率膜上部に形成した第1の絶縁膜を、第1のゲート電極を除去した後に除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】CMISのソース・ドレイン領域端部における転位の発生および拡散抵抗の上昇を防止する。

【解決手段】CMISにおけるソース・ドレイン領域12、14の形成時、シリコン基板1に不純物をイオン注入する前に、Pウエル層4には転位抑制元素としてアルゴンを打ち込み、かつNウエル層5には窒素を転位抑制元素として打ち込む。これにより転位の発生を抑制しつつ、かつ、Pウエル層4とNウエル層5それぞれに適した転移抑制元素を打ち分けることで拡散抵抗の上昇を抑制し、歩留まりを向上させ、素子の信頼性を高めることができる。

(もっと読む)

半導体装置

【課題】高電位側スイッチ素子の十分な駆動電圧を実現した半導体装置を提供する。

【解決手段】スイッチPMOSは、低電位側の出力MOSがオンのときにオンとなり、ブートストラップ容量(以下、容量という)を電源電圧に充電し、この出力MOSがオフのときにオフとなり、オンとなる高電圧側出力MOSを通した入力電圧と容量に蓄積された電圧が加算されて昇圧電圧が形成される。スイッチPMOSのソース領域およびドレイン領域は、逆の導電型を有するウェル領域内に形成される。容量で形成された昇圧電圧が電源電圧より高くなった時に、一方のソース領域またはドレイン領域とウェル領域によって形成される寄生ダイオードに対し逆方向電圧が印加されるように、スイッチPMOSの一方のソース領域またはドレイン領域およびウェル領域が容量の昇圧電圧側に接続されている。

(もっと読む)

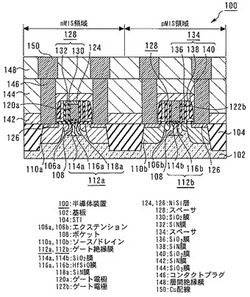

半導体集積回路装置の製造方法

【課題】金属シリサイド層と窒化シリコン膜の界面に自然酸化膜が残存していると、窒化シリコン膜の成膜後の種々の加熱工程(例えば種々の絶縁膜や導体膜の成膜工程のように半導体基板の加熱を伴う工程)において、金属シリサイド層表面にある自然酸化膜の酸素に起因して、金属シリサイド層が部分的に異常成長してしまう。

【解決手段】本願発明においては、集積回路を構成する電界効果トランジスタのソース・ドレイン上のニッケル・シリサイド等の金属シリサイド膜の上面に対して、不活性ガスを主要な成分とするガス雰囲気中において、実質的にノン・バイアス(低バイアスを含む)のプラズマ処理を施した後、コンタクト・プロセスのエッチング・ストップ膜となる窒化シリコン膜を成膜することにより、金属シリサイド膜の不所望な削れを生じることなく、金属シリサイド膜の上面の自然酸化膜を除去することができる。

を図ることができる。

(もっと読む)

半導体装置

【課題】チャージポンプの基数を変更しなくてもメモリセルに十分な電流量を供給することが可能な半導体装置を提供すること。

【解決手段】外部電源電圧判定回路2は、外部電源の電圧値を判定する。制御回路1は、外部電源電圧判定回路2によって判定された外部電源の電圧値がしきい値以下の場合に、チャージポンプ31による充電時間を変更してメモリセルに対するオペレーションを制御する。したがって、チャージポンプの基数を変更しなくてもメモリセルに十分な電流量を供給することが可能となる。

(もっと読む)

電源システム

【課題】比例制御型の電流制御を用いることにより、初期値設定誤差による誤差電流出力を最小にし、昇降圧コンバータにおける軽負荷時の効率を向上させる。

【解決手段】昇降圧DC−DCコンバータの間欠モードにおいて、目標指令値を、基準電圧Vref0から電圧ΔVrefだけ高い値に設定してステップ応答させる。そして、出力電圧Voの上昇過程において、出力電圧Voが任意のしきい値電圧まで到達したら、制御ロジック部30は、トランジスタ38〜41をすべてOFFして出力をハイインピーダンスにする。ハイインピーダンス中、負荷電流によって出力電圧Voが低下し、基準電圧Vref0に到達したら再度、トランジスタ38〜41の駆動制御を行う。これを繰り返し、出力電圧Voを一定値に制御する。

(もっと読む)

スケルチ回路

【課題】入力信号に高周波成分が含まれていても、安定した検出が可能なスケルチ回路を提供する。

【解決手段】閾値生成器7は、閾値信号を出力する。ミキサ回路5は、少なくとも入力信号が変化するタイミングで変化する信号で閾値信号を変調する。比較器6は、入力信号と変調された閾値信号とを比較して、入力信号が送信側から伝送された有効な信号であるか、あるいはノイズであるかを表わすスケルチ信号を出力する。

(もっと読む)

半導体集積回路

【課題】半導体集積回路の製造プロセスがばらつきを持っても所望の周波数特性を有するPLLを提供する。

【解決手段】PLLと制御ユニット9を具備し、PLLは位相周波数比較器1、ループフィルタ3、電圧制御発振器(VCO)8、分周器6を含み、VCO(8)は電圧電流変換器(VIC)とリング発振器を含む。制御電圧Vcに応答してVICは、リング発振器の動作電流を設定する制御電流を生成する。制御ユニット9は、PLLをオープンループのキャリブレーション動作期間とクローズドループの通常動作期間に切り換える。通常動作期間でVCOに所定の制御電圧Vcが供給され、VCOの周波数は所定の周波数とされる。キャリブレーション動作期間で制御電圧Vcと略等しいレベルの基準電圧VREFが供給された状態のVCOの周波数計測の間にVCOの周波数が所定の周波数と略等しくなるように、制御ユニット9はVIC81の動作パラメータTの値を設定する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置のバーンイン試験を行うソケットを複数備えたバーンインボードにおいて、各ソケットをバーンインボードから取り外すことなく、一括して洗浄する。

【解決手段】バーンインボード10が備える複数のソケット7は、それぞれ半導体装置を収容する窪みが形成された収容部8が配置される上面、収容部8内に配置され、バーンイン試験の際に半導体装置の外部端子と接触して通電するコンタクトピンを、それぞれ有している。ここで、ソケット7の洗浄工程では、洗浄液18aが充填された洗浄槽18に複数のソケット7の上面側が洗浄液18aに浸るように、バーンインボード(配線基板)10を洗浄槽18に配置して、複数のソケット7の上面にそれぞれ形成された収容部8内の気体を排気ノズル18cを用いて収容部8の外に排出する。

(もっと読む)

マスク欠陥検査方法および半導体装置の製造方法

【課題】波長が13.5nm付近の極端紫外(Extreme Ultra Violet:EUV)光を露光光源とする反射型マスクの欠陥修正技術を利用した半導体装置の製造技術を提供する。

【解決手段】ウエハ主面上に塗布されたフォトレジスト膜にマスクパターンを転写する際、アンダードーズあるいはデフォーカスまたはその両方の、オフコンディション条件で転写をした後、フォトレジスト膜に転写されたパターンを電位制御型外観検査用走査型電子顕微鏡(Scanning Electron Microscope:SEM)で検査する工程を経て欠陥検査する。これにより、マスク検査では容易に検査できないホールパターンにおける、多層膜位相欠陥を容易かつ実用的なスループットで外観検査が可能となり、欠陥の原因の分類に応じた欠陥救済を行った無欠陥マスクを供給することで歩留まりが向上する。

(もっと読む)

91 - 100 / 4,790

[ Back to top ]