株式会社ルネサステクノロジにより出願された特許

1,051 - 1,060 / 4,790

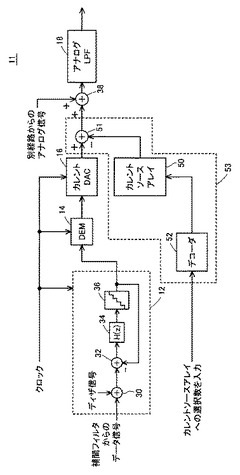

D/Aコンバータ

【課題】アイドルトーンを抑制するとともに、オフセット電圧を高精度にキャンセルすることが可能なD/Aコンバータを提供する。

【解決手段】カレントDAC回路16とアナログLPF回路18との間に調整回路53を設ける。調整回路53は、デコーダ52と、カレントソースアレイ50と、減算器51とを含む。デコーダ52は、カレントソースアレイの選択数を入力し、カレントソースアレイの選択数の入力に基づいて、カレントソースアレイ50は駆動される。減算器51は、カレントDAC回路16の出力信号とカレントソースアレイ50の出力信号とを減算して加算器38に出力する。

(もっと読む)

半導体装置

【課題】本発明は、MOSトランジスタの電流駆動能力をより向上させることができる半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板1、PMOSトランジスタP1、およびSiC層10を備えている。半導体基板1は、シリコンから成る。PMOSトランジスタP1は、半導体基板1の上面内に形成される。SiC層は、PMOSトランジスタP1のチャネル領域の下方から、PMOSトランジスタP1を構成する電極領域内若しくは電極領域下に渡って、形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の製造において、細線化したゲート電極上のシリサイドにおける凝集の防止および当該シリサイドの薄膜化を両立する。

【解決手段】NMOSトランジスタのゲート電極12並びにソース・ドレイン領域15の上部、およびPMOSトランジスタのゲート電極22並びにソース・ドレイン領域25には、それぞれNiシリサイド膜12s,15s,22s,25sが自己整合的に形成されている。Niシリサイド膜12s,15s,22s,25sは、NiおよびSiを主成分とし、化学量論組成がNiSiあるいはNiSi2である。但しそれらはPt,V,Pd,Zr,Hf,Nbのうち1以上の元素を合計で10at%未満の固溶量で含んでいる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置を高集積化および高性能化することのできる技術を提供する。

【解決手段】SOI−MISFETは、SOI層3と、SOI層3上にゲート絶縁膜15を介して設けられたゲート電極35aと、ゲート電極35aの両側壁側のSOI層3上に、SOI層3からの高さがゲート電極35aよりも高く設けられ、ソース・ドレインを構成する積上げ層24とを有している。また、バルク−MISFETは、シリコン基板1上にゲート絶縁膜15より厚いゲート絶縁膜16を介して設けられたゲート電極35bと、ゲート電極35bの両側壁側の半導体基板1上に設けられたソース・ドレインを構成する積上げ層25とを有している。ここで、積上げ層24の厚さが、積上げ層25の厚さよりも厚く、ゲート電極35a、35bの全体、SOI−MISFETのソース・ドレインの一部、およびバルク−MISFETのソース・ドレインの一部がシリサイド化されている。

(もっと読む)

半導体洗浄用組成物およびこれを用いた半導体装置の製造方法

【課題】アルミニウム合金配線層にエッチングなどのダメージを与えることなく、側壁堆積物やレジスト残渣を洗浄除去できる半導体洗浄用組成物並びに、その半導体洗浄用組成物を用いた半導体素子の製造方法を提供する。

【解決手段】有機酸とアンモニアとフッ素化合物の混合水溶液からなることを特徴とする半導体洗浄用組成物を用いる。また、無機酸とフッ素化合物の混合水溶液からなることを特徴とする半導体洗浄用組成物を用いる。さらにこれらの半導体洗浄用組成物を用いてアルミニウム合金から構成される金属配線層3の側壁堆積物6やレジスト残渣を洗浄除去する工程を有する。

(もっと読む)

カットオフ周波数自動調整回路及び携帯情報端末

【課題】本発明の目的は、使用する容量比の大きなフィルタカットオフ周波数を自動調整すること、並びにその自動調整にかかる時間を短縮することにある。

【解決手段】チャネルフィルタ回路の帰還容量及び不帰還容量(接地容量)ごとにフィルタカットオフ周波数自動調整回路及び誤差修正用のレジスタを設ける。これにより、帰還容量及び不帰還容量の容量差による誤差の拡大を招くことなく、フィルタカットオフ周波数の調整が可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】性能を損なうことなく、さらに余分な製造工程を追加することなく、容量素子の面積を縮小した半導体装置の技術を提供する。

【解決手段】第1容量絶縁膜を介して設けられた半導体基板の活性領域と、選択用nMISの選択ゲート電極と同一層の導体膜からなる下部電極CGcbとの間で第1容量部を構成し、電荷蓄積層を含む多層構造の絶縁膜と同一層の第2容量絶縁膜を介して設けられた下部電極CGcbと、メモリ用nMISのゲート電極と同一層の導体膜からなる上部電極MGctとの間で第2容量部を構成し、第1容量部と第2容量部とから積層型容量素子C1を構成し、下部電極CGcbの平面形状を、第1の間隔S1を設けて第1の幅W1の線状の導体膜が第1の方向に沿って複数本形成され、第2の間隔S2を設けて第2の幅W2の線状の導体膜が第1の方向と交差する第2の方向に沿って複数本形成された格子形状とする。

(もっと読む)

半導体装置の製造方法

【課題】金属シリサイド層の異常成長を防止する。

【解決手段】半導体基板1にゲート絶縁膜5、ゲート電極6a,6b、ソース・ドレイン用のn+型半導体領域7bおよびp+型半導体領域8bを形成する。それから、サリサイド技術によりゲート電極6a,6bおよびソース・ドレイン領域上に金属シリサイド層13を形成する。そして、金属シリサイド層13の表面を還元性ガスのプラズマで処理してから、半導体基板1を大気中にさらすことなく、金属シリサイド層13上を含む半導体基板1上に窒化シリコンからなる絶縁膜21をプラズマCVD法で堆積させる。

(もっと読む)

不揮発性半導体記憶装置

【課題】不揮発性半導体記憶装置の消去/書込耐性を改善し、gm劣化によるメモリセルが存在する場合にも、消去/書き込み耐性の低下を抑制することのできる不揮発性半導体装置を提供する。

【解決手段】消去対象の選択メモリセルの消去および書き戻し後の閾値電圧の上限値を満たしているかを判定する過書き戻しベリファイ時に、同一列かつ異なるメモリセルを並行して選択し、これらの選択メモリセルの記憶データに従って判定を行うベリファイ制御回路を備える。

(もっと読む)

半導体装置

【課題】動作時におけるトランジスタのリーク電流を低減することが可能な半導体装置を提供する。

【解決手段】半導体装置は、クロックに同期した信号を受ける入力ノードINに結合される制御電極と、出力ノードOUTに結合される第1導通電極と、第2導通電極とを有する第1のトランジスタM1,M2と、入力ノードINに結合される制御電極と、出力ノードOUTに結合される第1導通電極と、電源ノードに結合される第2導通電極とを有する第2のトランジスタM3,M4と、電源ノードと第2のトランジスタM3,M4の第2導通電極との間に接続され、クロックの周波数の検出結果を示す第1の制御信号VDETに基づいてオン・オフされる第1のスイッチ素子CM1とを備える。

(もっと読む)

1,051 - 1,060 / 4,790

[ Back to top ]