株式会社ルネサステクノロジにより出願された特許

1,071 - 1,080 / 4,790

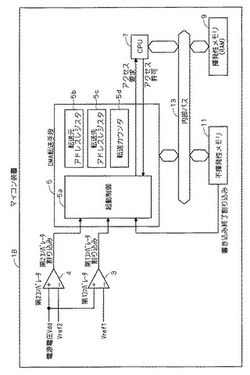

マイコン装置

【課題】電源電圧が基準電圧よりも低下したときに、揮発性メモリ内のデータを不揮発性メモリに速やかに退避できるマイコン装置を提供する。

【解決手段】CPU7と揮発性メモリ9と不揮発性メモリ11とがバス接続されてなるマイコン装置1Bにおいて、電源電圧Vddと第1基準電圧Vref1とを比較し、電源電圧Vddが第1基準電圧Vref1よりも低下した時に割込要求信号を出力する第1コンパレータ3と、電源電圧Vddと第2基準電圧Vref2とを比較し、電源電圧Vddが第2基準電圧Vref2よりも低下した時に割込要求信号を出力する第2コンパレータ4と、第1コンパレータ3からの前記割込要求信号と第2コンパレータ4からの前記割込要求信号に応じて起動し、バス13経由で揮発性メモリ9内のデータを不揮発性メモリ11に転送するDMA転送手段5とを備える。

(もっと読む)

半導体装置の製造方法

【課題】ウエハ表面の検査結果はいわゆるウエハ・マップ・データとして表示画面に表示可能な形で電子情報処理システムに格納され、後の処理に活用される。従って、裏面検査の結果もウエハ・マップ・データに反映する必要があるが、欠陥や不良のあった裏面の位置と対応する表面の位置を検査者が判断して当該不良情報をウエハ・マップ上に登録する必要がある。しかし、このような表裏の対応付け作業はウエハの大型化に伴い著しく困難なものになってきている。

【解決手段】本願発明はウエハ・プロセス完成時の外観検査において、ウエハ裏面の不良位置と対応するウエハ表面の位置を自動的に対応させることで、ウエハ裏面の外観不良データのウエハ・マップ・データへの反映を確実にするものである。

(もっと読む)

RF増幅装置

【課題】トランジスタの出力電極とインピーダンス整合回路としての伝送線路変圧器TLTとを接続する際にTLTのインピーダンス整合の条件を維持すること。

【解決手段】RF増幅装置は、アンテナに供給される送信電力を生成するトランジスタQの出力電極に接続された伝送線路変圧器TLTを具備する。TLTの主線路Loutの一端In(A)にはトランジスタの出力電極からの送信電力が供給され、TLTの副線路Linの一端Lin(B)は交流接地点に接続される。副線路の他端Lin(A)は主線路の一端に接続され、主線路の他端Out(A)からアンテナに供給される送信電力が生成される。TLTの主線路と副線路とが近接して対向したエネルギー結合部では、副線路から主線路へ結合エネルギーが伝達される。トランジスタの出力電極と電気的に接続された接続部材BWは、エネルギー結合部の一部の主線路と副線路との一方に形成された接続部CPと接続される。

(もっと読む)

フォトマスクの製造方法

【課題】フォトマスクの製造難易度を定量的に表現し、フォトマスクを効率的に製造できる技術を提供する。

【解決手段】マスク製造負荷予測システムによる計算で求めたマスク製造負荷指数でマスクレイアウト、製品およびマスク層ごとに異なるマスク製造難易度を相対的に把握し、レイアウト修正可能な段階では最終的なレイアウトを難易度の低いものに修正し、マスク発注者からマスク製造者に早いタイミングでマスク製造難易度に関する情報を提供する。マスク製造負荷指数は、欠陥保証負荷指数と描画負荷指数とで示す。

(もっと読む)

半導体装置および半導体集積回路装置

【課題】半導体集積回路装置の高集積化及び低コスト化を可能にする複数のトランジスタセルを含む半導体装置を提供することを第1の目的とし、高密度に集積化された小型の半導体集積回路装置を安価に提供する。

【解決手段】基板上に、それぞれ第1層、ベース層、及び、第2層を順に有し、前記第1層、及び、前記第2層の一方がコレクタ層であり、他方がエミッタ層であるトランジスタセルを複数含み、前記各トランジスタセルの前記第1層に接続される第1電極が、前記第1層に形成されたエッチング溝に形成された半導体装置において、前記エッチング溝は、その長手方向に沿った側面が順メサ面となっており、複数のトランジスタセル間の前記第1電極が、前記各順メサ面に交差するように設けられた、まとめ配線によって接続される半導体装置である。

(もっと読む)

半導体装置の製造方法

【課題】シリサイド層を備える半導体装置において、シリコン基板と不純物拡散層との間の接合リーク電流を低減することを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、(a)シリコン基板1表面に不純物拡散層5,8を形成する工程と、(b)不純物拡散層のうち第2の不純物拡散層8上に、ニッケルからなる金属膜9を形成する工程とを備える。そして、(c)窒素濃度が80%以上の雰囲気で、スパッタによりチタンを含むチタンナイトライド膜10を金属膜9上に形成する工程を備える。そして、(d)工程(c)の後に、熱処理により第2の不純物拡散層8のシリコンと、ニッケルとを反応させてシリサイド層11を形成する工程を備える。

(もっと読む)

モータ制御装置および電動車両

【課題】容易に又は効率的に高機能化を実現可能なモータ制御装置を提供する。

【解決手段】例えば、モータ制御装置IC内に、スロットル電圧THRTLに基づいてPWM信号を生成するPWMコンパレータ部PWMCMP1と、PWM信号を用いてインバータ部IV_BKを所定のシーケンスで制御するPWM制御部PWM_CTL等に加えて、FV変換部FVCおよび外部端子P9を設ける。FVCは、モータ部MTのホールセンサからの周波数信号を受け、この周波数信号の周期をカウントし、その逆数を演算した結果をアナログ電圧に変換することで、周波数に比例した速度電圧信号FVをP9より出力する。このP9にはスピードメータ等が直接接続される。さらに、FVCは、車両速度を一定に保つクルーズコントロール部CRUS等でも利用される。

(もっと読む)

半導体装置

【課題】同一チップ内に不揮発性メモリを備える半導体装置において、集積度を向上させる。

【解決手段】共通の浮遊電極FGを備える書き込み/消去用素子WDと、読み出し用トランジスタQRと、MISキャパシタCとを有する不揮発性メモリセルNVMにおいて、上記書き込み/消去用素子WDと読み出し用トランジスタQRとは、半導体基板1の主面S1上に配置された同一のp型の動作素子形成用pウェルPW1内において、電気的に接続されるようにして形成され、上記MISキャパシタCは、動作素子形成用pウェルPW1と分離され、かつ、動作素子形成用pウェルPW1に沿うようにして配置されたp型のキャパシタ形成用pウェルPW2内に形成されていることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】装置を小型化してもリードの脱落を防ぐことができる半導体装置の製造方法を得る。

【解決手段】リード11の上面にハーフエッチにより凹部17´が形成されたリードフレーム18を準備する。ダイパッド13上に半導体チップ14を搭載する。樹脂16で一括封止する。樹脂16で封止したリードフレーム18をブロック19ごとに分離する。樹脂封止工程において、凹部17´を樹脂16で上方から充填し、リード11の下面を樹脂16から露出させる。ダイシング工程において、リード11の切断面が凹部17´にくるようにして、リード11の上面と切断面との間に切り欠き17を形成する。この切り欠き17には樹脂が充填されるためリードの脱落が防止される。

(もっと読む)

半導体素子の製造方法

【課題】半導体ウェハの大口径化に伴う素子バラツキを低減させた半導体素子の製造方法を提供する。

【解決手段】半導体ウェハ上に同一区画が碁盤目状に形成される。上記各区画には、同一の特性を持つようにされた半導体素子を形成する半導体領域を形成するために不純物がデポジションされる。上記半導体ウェハの上記デポジションされた不純物は、拡散炉により拡散される。上記拡散炉での熱処理による上記半導体ウェハの熱バラツキによるPN接合容量のバラツキは、上記不純物がデポジションされら半導体領域の面積を異なせることにより補正する。

(もっと読む)

1,071 - 1,080 / 4,790

[ Back to top ]