株式会社ルネサステクノロジにより出願された特許

151 - 160 / 4,790

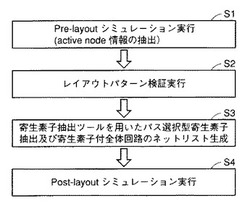

バックアノテーション装置

【課題】効率的にバックアノテーションを実行する。

【解決手段】Pre-layoutシミュレーションを実行し、シミュレーション実行時に電位の変化したノード(アクティブノード)を抽出する(S1)。レイアウトパターンデータに対してレイアウトパターン検証を行なう(S2)。S1のPre-layoutシミュレーション時に抽出されたアクティブノード情報に基づいて、レイアウトパターンデータより寄生素子が抽出され、レイアウトパターンデータのすべてのデバイスと抽出された寄生素子情報を含んだ寄生素子付ネットリストが生成される(S3)。生成されたネットリストに基づいてPost-layoutシミュレーションが実行される(S4)。

(もっと読む)

半導体装置

【課題】第1の半導体チップ上に第2の半導体チップが搭載される際に、第1の半導体チップがリードフレームと衝突することを防止する。

【解決手段】リードフレームは、ダイパッドと、ダイパッドを支持する吊リードSLとを有する。接合部JPはリードフレーム上に設けられている。第1の半導体チップC1は接合部JPを介してリードフレーム上に設けられている。第2の半導体チップC2は第1の半導体チップC1上に設けられている。樹脂部材はダイパッドと第1および第2の半導体素子C1、C2とを覆っている。接合部JPはダイパッドおよび吊リードSLの各々の上に位置している。

(もっと読む)

半導体集積回路装置

【課題】ラッチ型メモリセルのラッチ部のサイズを増大させることなく、データ保持特性を改善する。

【解決手段】ラッチ型メモリセルの記憶ノードを構成するゲート電極配線(21a,21c)と交差する方向に、フラッシュメモリセルトランジスタの固有の配線と同一配線層の導電線(26a,26b)を連続的に延在させて配置する。ゲート電極配線と導電線の交差部において容量を形成し、導電線を固定電位に維持する。

(もっと読む)

通信装置、通信携帯端末、及び非接触ICカードのためのリーダライタ

【課題】負荷変調の結果が負荷変調信号の位相又は振幅に現れなくなる現象があってもパケットの全域において変調データを正確に復調可能にする。

【解決手段】負荷変調信号の振幅変化を検出する振幅検波回路(30)と、負荷変調信号の位相変化を検出する位相検波回路(31)とを設け、夫々の検波信号に対するデコード信号の正規性を、情報ビットの正規デューティに基づいて逐次判定し、予め指定された一方のデコード信号に対する正規性が検出されている間は当該一方のデコード信号を選択し、非正規性が検出されたときはデコード信号の選択を前記一方から他方のデコード信号に切換える選択制御を行い、この選択制御を経て得られるデコード信号に対して、エラーチェック及びデータバッファへの蓄積を行うようにする。このように、検波信号の正規生を情報ビットのデューティの正規性から逐次判定する。

(もっと読む)

半導体装置の製造方法および半導体洗浄用組成物

【課題】熱酸化シリコン膜、非ドープCVD酸化シリコン膜、多結晶シリコン膜、窒化シリコン膜を含む積層膜に対して、常温において洗浄時の各種膜に対するエッチング量差を低減し、また、各種膜に対するエッチング速度を適度に制御することを可能とする。

【解決手段】半導体基板の主面上に絶縁層を形成する工程と、前記絶縁層の上に導電層を堆積する工程と、前記導電層の上にフォトレジスト膜を形成する工程と、前記絶縁層および前記導電層をエッチングすることによってゲート素子を形成する工程と、前記フォトレジスト膜を除去した前記半導体基板の主面を半導体洗浄用組成物によって洗浄する工程と、前記半導体洗浄用組成物のリンス処理および乾燥処理を行う工程とを含む半導体装置の製造方法であって、前記半導体洗浄用組成物は、フッ化アンモニウムと、フッ化水素酸と、過酸化水素と、脂肪族第1級アミンとを含む20℃〜28℃の混合水溶液からなる。

(もっと読む)

半導体集積回路装置

【課題】定格電圧よりも大きい入力信号があっても、ループフィルタ内に大信号を通過させずに積分器をリセットして次数低減を行い、速やかな通常動作への復帰を実現する。

【解決手段】入力信号が、基準電圧Vref_pよりも高くなり、定格電圧よりも大きくなると、検出器22からHi信号の検出信号Cp/Cnが出力される。これを受けて、リセット制御コントローラ23から、リセット制御信号RCが出力される。これにより、積分器10〜13がリセットされ、大信号レベルの入力信号がループフィルタ内を通過することを防止することができる。このとき、スイッチ24がONとなり、デルタシグマ型A/D変換器4の入力から量子化器14の入力へ信号パスが形成されることになり、大信号入力レベル時であっても、後段のDSP5へA/D変換信号を伝達させてAGCを動作させる。

(もっと読む)

半導体装置およびその製造方法

【課題】電界効果トランジスタを有する半導体装置を高性能化する。

【解決手段】n型のシリコン基板1に形成されたMISトランジスタQ1を有する半導体装置であって、主面s1に形成されたn型ドリフト領域n1と、主面s1からn型ドリフト領域n1の途中にまで深さ方向に向かって形成され、ゲートトレンチtr1とダミートレンチtr2とを有する複数のトレンチ2と、ゲートトレンチtr1の内部にゲート絶縁膜IGを介して形成されたゲート電極EGと、ダミートレンチtr2の底部周辺のn型ドリフト領域n1に形成されたp型柱状領域pcとを有する。ゲートトレンチtr1とダミートレンチtr2とは互いに同程度の深さであり、互いに並んで配置され、p型柱状領域pcは、n型ドリフト領域n1内において深さ方向に向かって延在するようにして形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】リーク電流を低減することが可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、第1導電型領域2を含む半導体基板1の主表面に形成された分離絶縁膜4と、第1および第2の電界効果型トランジスタ38a、38bとを備える。第1および第2の電界効果型トランジスタ38a、38bは、分離絶縁膜4に隣接するように形成された第2導電型領域11bと、ゲート電極6aと、ゲート電極の側面に形成された下層サイドウォール膜31aと、この下層サイドウォール膜上に形成され、下層サイドウォール膜とは異なる材料を含む上層サイドウォール膜20aと、第2導電型領域上に形成された高融点金属シリサイド層8cとを含む。分離絶縁膜4の上部表面は、第1導電型領域2と第2導電型領域11bとの接合界面よりも上に位置する。

(もっと読む)

半導体装置

【課題】抵抗素子の抵抗値の基板電圧依存性をなくす。

【解決手段】基板領域(25A,25B)上に互いに直列に接続される抵抗素子(R1、R2)において、抵抗素子の基板領域と対応の抵抗素子の間の平均電位が逆極性でかつ大きさが等しくなるように、抵抗素子端部と対応の基板領域とをバイアス配線(27A,27B)で接続する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極の形成後に熱処理が施される場合でも、金属から成るゲート電極の仕事関数を比較的容易に制御することができる半導体装置の製造方法を提供する。

【解決手段】nFET領域RnおよびpFET領域Rpの半導体基板1上にゲート絶縁膜2およびゲート電極用金属膜3を順次に形成した後、pFET領域Rpに形成されたゲート電極用金属膜3に不純物を注入する。これによって、pFET領域Rpに形成されたゲート電極用金属膜3の組成を変化させることができるので、このゲート電極用金属膜3で形成されるpFET領域Rpのゲート電極の仕事関数を変化させることができる。したがって、nFET領域RnとpFET領域Rpとに、異なる仕事関数を有するゲート電極を容易に形成することができる。

(もっと読む)

151 - 160 / 4,790

[ Back to top ]