株式会社ルネサステクノロジにより出願された特許

171 - 180 / 4,790

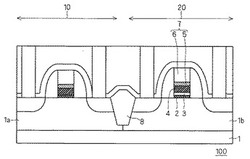

半導体装置およびその製造方法

【課題】良好な形状のsingle metal/dual high−k構造を形成し、nMOS、pMOSそれぞれに適したフラットバンド電圧を得ることができる半導体装置を得ること。

【解決手段】本発明の一実施形態における半導体装置100は、第1導電型のMOSFET10と、第2導電型のMOSFET20を有する。第1および第2導電型のMOSFET10,20は、半導体基板1上に形成された第1の絶縁膜2と、第1の絶縁膜2上に形成され、第1の絶縁膜2よりも誘電率の高い絶縁材料からなる第2の絶縁膜4と、第2の絶縁膜4上に形成され、第2の絶縁膜4に拡散して仕事関数を制御する材料を含むメタル層5を下層に有するゲート電極7と、を備える。また、第2導電型のMOSFET20は、第1の絶縁膜2と第2の絶縁膜4との間に形成され、仕事関数を制御する材料が第1の絶縁膜2界面に拡散するのを防止する拡散防止膜3をさらに備える。

(もっと読む)

磁場制御構造

【課題】本発明は、磁場制御構造に関し、特に、集積回路を構成する基板上に渦電流が発生しないように磁力線を制御する磁場制御構造に関する。

【解決手段】本発明による磁場制御構造は、集積回路における磁場制御構造であって、磁場を発生させる磁場発生源1、2と、磁場発生源1、2の近傍に、または磁場発生源1、2に接して配置された磁性体3とを備え、磁性体3によって磁場発生源1、2からの所定方向の磁力線を吸収することを特徴とする。

(もっと読む)

画像復号方法、画像復号装置、画像符号化方法及び画像符号化装置

【課題】処理対象画像データの特徴に応じて可変長符号化による圧縮効率を向上する。

【解決手段】量子化されたデータを可変長符号化して圧縮する装置であって、符号化済みの画像データの統計情報(MBTyp、CBPL)を格納する統計情報格納メモリ(212)と、前記統計情報格納メモリに格納された統計情報に基づいて可変長符号表を生成する可変長符号表生成部(213)と、前記可変長符号表生成部で生成した可変長符号表に基づき可変長符号化を行う可変長符号化部(205)と、を備える。前記可変長符号表生成部は、符号化済みの画像データの所定範囲内で算出した統計情報の生起確率と、符号化パラメータに基づいて選択された初期生起確率とを加算し(S3005)、加算して得られた生起確率の高い統計情報の順に短い符号を割り当てて(S3006)、可変長符号表を生成する。

(もっと読む)

記憶装置

【課題】ライトディスターブおよびリードディスターブの問題を解決し信頼性が高められた記憶装置を提供する。

【解決手段】相変化メモリにデータを書込む際にステップS4で一旦データを読出す。続いてステップS5に進み読出データが“1”か“0”かが判断される。読出データが“0”であった場合にはステップS6に進み、メモリセルに対して“1”を書込むために電流の印加が行なわれる。一方、ステップS5において読出データが“1”であると判断された場合には、書込動作は行なわれずステップS10に進む。好ましくは、書込みデータが“0”の場合には、データ読出を行なわずにデータ“0”を書込む。高抵抗状態(“1”を保持している状態)への“1”の再書込を行なわないから、メモリセルの抵抗比が大きくとれるようになり、読出信号が大きくでき、読出アクセスタイムを高速にすることができる。

(もっと読む)

送信器及び携帯情報端末

【課題】連続的に送信を行い続けるUMTS等においても動的にDCオフセットの補正を行える送信器を提供する。

【解決手段】送信器中に直交変調器を2以上配置し、送信スロット毎に直交変調器を切り替えて送信を行う。連続した2以上の送信スロットで特定の直交変調器が用いられることは無いため、特定の直交変調器が送信を担当しない期間中にDCオフセットキャリブレーション対象となり、DCオフセット制御回路129がDCオフセットキャリブレーション対象に対してDCオフセットのキャリブレーションを実行する。

(もっと読む)

マイクロコンピュータ

【課題】デバッグツール2から直接に内蔵フラッシュメモリ5の書き換え制御を行うことができ、デバッグの作業効率を高くすることが可能なマイクロコンピュータを得る。

【解決手段】CPU3によって、内蔵フラッシュメモリ5に格納された内蔵フラッシュ情報をJTAGインタフェース11を介してデバッグツール2から読み出し可能にし、デバッグツール2からその内蔵フラッシュ情報に基づいた書き換みデータをJTAGインタフェース11を介して入力して、さらに、CPU3によって、内蔵フラッシュメモリ5に格納された書き換えプログラムに基づいて書き換みデータを内蔵フラッシュメモリ5に書き換える。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜に所望の大きさでバーズビークが形成され、ゲート絶縁膜の電気的特性に優れた半導体装置およびその製造方法、を提供する。

【解決手段】半導体装置の製造方法は、シリコン基板1上にトンネル酸化膜3およびポリシリコン膜4を形成する工程と、ポリシリコン膜4、トンネル酸化膜3およびシリコン基板1をエッチングしてトレンチ2m,2nを形成する工程と、サイドウォール41をトレンチ2m,2nの側面に形成する工程と、シリコン基板1をエッチングしてトレンチ42m,42nを形成する工程と、サイドウォール41が存在する状態で、トレンチ42m,42nの内壁、ならびにサイドウォール41と対向するトンネル酸化膜3の端部に隣接したポリシリコン膜4およびシリコン基板1の部分を酸化し、トンネル酸化膜3の端部にバーズビーク部11,12を形成する工程とを備える。

(もっと読む)

PLL回路

【課題】PLL回路において、アナログ回路のデジタル化によって生じる量子化雑音を抑制することができる技術を提供する。

【解決手段】基準信号REFと分周後の信号DIVとの位相及び周波数を比較してデジタル値に変換するデジタル位相周波数比較器(DPFD)101と、デジタル位相周波数比較器101の出力から高周波雑音成分を除去するデジタルループフィルタ(DLF)102と、デジタルループフィルタ102の出力のデジタル値をアナログ値に変換するデジタルアナログ変換器(DAC)105と、デジタルアナログ変換器105の出力から高周波雑音成分を除去するアナログフィルタ(AnF)106と、アナログフィルタ106の出力に基づいて周波数が制御される電圧制御発振器(VCO)103と、電圧制御発振器103の出力を分周し、分周後の信号DIVを出力する分周器(DIV)104とを備える。

(もっと読む)

MRAM制御装置およびMRAM制御方法

【課題】MRAMからの読み出し回数を増やさず、システム全体の電流量を低減することができるMRAM制御装置を得ること。

【解決手段】MRAMの書込みを制御するMRAM制御装置であって、書込み要求に含まれるデータを、書込みアドレスと書込み要求回数を示す頻度情報と対応づけて保持するデータ保持メモリ61と、保持している書込みアドレスに対して書込みのあった回数を計数して頻度情報としてデータ保持メモリ61に格納する頻度算出回路62と、書込み要求に含まれる書込みアドレスと保持している書込みアドレスとを比較し、一致するアドレスがなく、空き領域が無い場合には、頻度情報に基づき頻度の小さいデータを選択し、選択したデータをMRAMへ書込み、そのデータが格納されていたデータ保持メモリ61の領域に、書込み要求に含まれるデータを書込む。

(もっと読む)

半導体装置およびその製造方法、ならびに電源装置

【課題】電界効果型トランジスタを備えた半導体装置において、チャネル抵抗を低減する。

【解決手段】厚さ方向に沿って互いに反対側に位置する第1主面S1および第2主面S2を持つ半導体基板1に、トレンチゲート型の電界効果型トランジスタを有する半導体装置であって、前記トレンチゲート型の電界効果型トランジスタは、前記第1主面S1側に第1半導体領域2と、前記第2主面S2側に第2半導体領域5と、その間に半導体ウェル領域3と、第2主面と交差する第1方向Aに延びるように形成された溝部9と、その内面にゲート絶縁膜6を介して形成されたゲート電極8とを備え、ゲート電極8の底部BGは第1半導体領域2にあり、ウェル底部BWは、ウェル深部DBWとウェル浅部SBWとを有し、ウェル深部DBWは、ゲート絶縁膜6に対して、ウェル浅部SBWよりも遠い領域にあることを特徴とする。

(もっと読む)

171 - 180 / 4,790

[ Back to top ]