株式会社ルネサステクノロジにより出願された特許

21 - 30 / 4,790

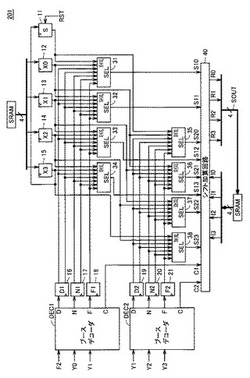

半導体装置

【課題】演算の高速化を図り、また、小型化を図ることで並列度を高めることが可能な半導体装置を提供する。

【解決手段】半導体装置201は、乗数を示す3ビットの第1の乗数データを受けて、ブースのアルゴリズムに従い、シフトフラグ、反転フラグおよび演算フラグを出力するデコーダDEC1,DEC2と、被乗数を示す2ビットの第1の被乗数データと、シフトフラグ、反転フラグおよび演算フラグとを受けて、シフトフラグに基づいて第1の被乗数データの上位ビットおよび下位ビットのいずれかを選択し、選択したビットを反転フラグに基づいて反転または非反転し、反転または非反転されたデータおよび所定の論理レベルのデータのいずれかを演算フラグに基づいて選択し、第1の乗数データおよび第1の被乗数データの部分積を示す部分積データとして出力する第1の部分積算出部31〜38とを備える。

(もっと読む)

半導体データ処理デバイス及びデータ処理システム

【課題】冗長構成の各データ処理ブロックが実行するプログラムを相違させること要さずに処置結果をデータ処理ブロック毎に異なる鍵(誤り訂正符号の生成論理)で符号化できるようにする。

【解決手段】データ処理ブロック(100a,100b)による処置結果を符号化するのにハードウェア回路を用いる。例えば、夫々のデータ処理ブロック毎に、固有の鍵(誤り訂正符号の生成論理104a,104b)を用いる符号化用のハードウェア回路(103あ、103b)を採用する。これによって、複数のデータ処理ブロックのプログラム動作を同じにすることを保証しつつ、夫々のデータ処理ブロックによる処理結果を外部で検証可能にする。したがって、データ処理ブロックのプログラム動作の結果に不一致を生じさせずに、データ処理ブロック固有の鍵を用いて外部検証用のデータを符号化することが可能となる。

(もっと読む)

表示駆動装置及び表示装置

【課題】階調度調整に代表されるような表示データに対する調整係数の演算処理に伴う電力消費を低減し、ディスプレイパネルの高解像度化にも容易に対応できる表示装置を提供する。

【解決手段】ディスプレイパネル(101)に駆動信号を出力する複数の駆動部(117〜120)を並列配置し、前記複数の駆動部の並列方向に沿って複数の第1演算部(107〜110)及び複数の表示RAM(111〜114)を配置しておき、外部から供給された表示データを複数の表示RAMに分配し、夫々の表示RAMから表示データを第2演算部(106)が並列に受け取って1画面分の画素データの階調分布のヒストグラムを解析し、解析結果に基づいて前記調整係数を演算する。演算された調整計数を夫々の第1演算部に返し、第1演算部は対応する表示RAMから読み出した表示データに調整計数を用いた演算を行ってディスプレイパネルの駆動データを生成する。

(もっと読む)

半導体装置

【課題】半導体装置に搭載された半導体チップにかかる応力を抑えて、半導体チップ内における膜の剥離やクラック等を防止する。

【解決手段】半導体チップと、半導体チップの主面に形成された電極と、半導体チップを搭載する配線基板とを備える半導体装置において、例えば、配線基板の配線と、電極とを電気的に接続する再配線を設ける。この再配線としては、半導体チップと配線基板との間に生じる応力を緩和するようなものを使用する。

(もっと読む)

LED駆動回路および半導体素子ならびに画像表示装置

【課題】LEDアレイに大電流を流す場合であっても実装面積の増大を抑制して定電流駆動することができ、また、定常動作時だけでなくデジタル調光時にも有効なLED駆動回路を提供する。

【解決手段】LEDアレイ100を駆動するLED駆動回路1であって、各LEDストリングにそれぞれ直列に接続され、各LEDストリングを定電流駆動するn個の縦型構造の定電流駆動素子50と、各LEDストリングに流れる電流が定電流となるように各定電流駆動素子50のオン電圧を制御するn個の定電流制御回路60と、各定電流駆動素子50におけるLEDストリング側の各端子電圧を入力として、各端子電圧のうちの最小電圧を選択し、前記最小電圧と所定の設定電圧との差分に基づいて指令信号80を出力する最小電圧検出回路30と、指令信号80に基づいてLEDアレイ100への印加電圧を初期設定電圧より小さい電圧に制御する電源制御回路20とを有する。

(もっと読む)

半導体集積回路装置

【課題】エリアバンプ構造の半導体チップに最適化したI/Oセルのレイアウトを施すことにより、チップサイズを縮小化する。

【解決手段】I/Oセル3は、半導体チップの辺側から中心側にかけて、信号電圧変換回路6、論理部7、プリバッファ部8、ESD保護部の抵抗30、出力バッファ部におけるトランジスタ28、ESD保護部の抵抗31、ESD保護部のダイオード32、パッド接続口3aを挟んでダイオード33、出力バッファ部におけるトランジスタ29、およびコアバッファ部5が直線状にレイアウトされている。プリバッファ部8をパッド接続口3aよりも半導体チップ辺側に配置することによって、該パッド接続口3aをI/Oセル3の中央部よりも半導体チップの中心側にレイアウトでき、半導体チップの辺部に最も近いパッドをI/Oセル3の領域からはみ出すことなくレイアウトできる。

(もっと読む)

クロストーク解析装置

【課題】クロストーク解析による解析結果の悲観性を削減することが可能なクロストーク解析装置を提供すること。

【解決手段】係数格納部29は、パスに含まれるネットの段数に応じて規定された係数を格納する。クロストーク値計算部24は、レイアウトデータ格納部28に格納されるレイアウトデータを参照して、パスにおける最悪条件のクロストークによって発生する遅延時間を計算する。係数抽出部25は、解析対象のパスに含まれるネットの段数を抽出し、係数格納部29に格納される係数の中から抽出された段数に対応する係数を抽出する。そして、遅延時間計算部26は、クロストーク値計算部24によって計算された遅延時間に係数を乗算する。したがって、クロストーク解析による解析結果の悲観性を削減することが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】MONOS方式を採用するスプリットゲート型メモリセルの情報保持特性を向上させる。

【解決手段】選択ゲート8の基板表面とメモリゲート15の基板表面に段差を設ける。選択ゲート8の基板表面がメモリゲート15の基板表面より下方にある場合、書込み時のチャネルの電子は段差部を斜めに流れる。斜めに流れている間にバリアを越えるのに必要なエネルギーを得ても、基板表面から離れているため、電子の注入は起こらない。注入は電子が基板表面に到達する位置よりドレイン領域56側でのみ可能となる。その結果、電子のギャップ領域への注入が抑制され、電子分布が正孔分布に近づくため、情報保持時のしきい値変動が抑制され、メモリセルの情報保持特性が向上する。

(もっと読む)

半導体装置の製造方法および半導体装置の製造装置

【課題】コレットの先端部が変形しても、コレットを交換することなく、ダイボンディング工程を行うことのできる技術を提供する。

【解決手段】半導体チップのピックアップと基材のチップ搭載部への半導体チップの接着とを繰り返した後、コレット5をダイボンディング装置1に備わるコレット加工治具へ移動させ、コレット5の先端部の吸着面を研磨ステージ上に装着したラッピングペーパで研磨して平坦に加工し、さらにコレット5の吸着面に付着した研磨粉を異物除去ステージ上に装着されたシリコンチューブ、またはシリコンシートおよびシリコンチューブで除去する。

(もっと読む)

EDAツール、半導体装置およびスキャンチェイン構成方法

【課題】スキャンチェイン上の隣接するFFの異なる論理値を持つ頻度が大きくなることでテスト時のIRドロップを回避する技術を提供する。

【解決手段】期待値導出処理モジュールM1が各FFの論理値を確率伝播の計算または論理シミュレーションの実施によって導出する。グルーピングモジュールM2は求めた論理値を参照して検査対象のFFをいくつかのグループにグルーピングする。スキャンチェイン構成モジュールM3は論理値「1」を取り込む頻度が背反する2つのグループをペアにして、一方を論理反転させて1つのスキャンチェインを構成する。

(もっと読む)

21 - 30 / 4,790

[ Back to top ]