株式会社ルネサステクノロジにより出願された特許

41 - 50 / 4,790

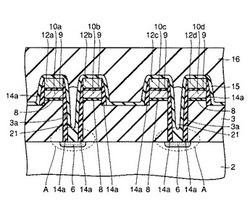

半導体装置

【課題】シリコン基板に結晶欠陥が発生するのを抑制して、動作の信頼性が確保され高い歩留まりが得られる半導体装置を提供する。

【解決手段】シリコン基板2に形成された溝にトレンチ分離酸化膜3が形成されている。そのトレンチ分離酸化膜3上にフローティングゲート電極10a〜10dおよびコントロールゲート電極12a〜12dが形成されている。フローティングゲート電極等によって挟まれた領域にシリコン基板2の表面を露出する開口部3aが形成されている。開口部3aを埋込むとともにコントロールゲート電極を覆うようにBPTEOS膜16が形成されている。BPTEOS膜16によって埋込まれた開口部3a内にボイド21が形成されている。

(もっと読む)

キャリア形状測定機

【課題】キャリアおよびキャリアに収容された半導体ウエハの姿勢を精度良く測定することのできる形状測定機を提供する。

【解決手段】測定対象であるキャリア18を支持するステージ12,20と、測定対象の形状を測定する測定部10とを有する。ステージ12,20は、キネマティックカップリングによって測定対象を支持するために、キネマティックカップリングピン20a,20b,20cを有する。

(もっと読む)

半導体パッケージ

【課題】所望のランド数を確保しながら、実装基板に確実に接続される半導体パッケージを提供する。

【解決手段】LGAパッケージでは、基板2の外周側に外周ランド群3が設けられ、内周側に内周ランド群4が設けられている。外周ランド群3では2列のランド3a,3bが配置され、内周ランド群4では2列のランド4a,4bが配置されている。各ランド3a,3b,4a,4bは、X方向とY方向とにピッチPをもって配置されている。外周ランド群3のランド3bと、その直近に位置する、内周ランド群4のランド4aとのX方向またはY方向の距離Lは、ピッチPの1.5倍とされる。

(もっと読む)

電流駆動型D/Aコンバータのバイアス回路

【課題】電流スイッチトランジスタの制御電圧によって生じるノイズをより小さくし、また、電流スイッチがオフする際に生じていたグランドもしくは電源電圧のノイズを低減し、高性能な電流駆動型D/Aコンバータを得る。

【解決手段】NMOSトランジスタM12P,M12N,M22P,M22N,M32P,M32Nがオフするオフ制御電圧(BIAS3)を、オン制御電圧(BIAS2)に近づけた電圧に設定したことにより、NMOSトランジスタの制御電圧振幅(オン制御電圧−オフ制御電圧)が小さくなり、寄生容量を介した電荷注入によるノイズの発生を低減すると共に、オフする際の寄生容量からグランドもしくは電源への放電電流の流れ込みによるグランド電圧もしくは電源電圧のノイズの発生を低減し、高性能な電流駆動型D/Aコンバータを得ることができる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】層間絶縁膜を表面研磨する工程を経て形成される半導体装置の信頼性を向上させる。

【解決手段】シリコン基板1の主面s1上に、高耐圧ゲート絶縁膜IG1および高耐圧ゲート電極EG1からなる高耐圧ゲートG1を形成した後、サリサイドブロック膜SAB、層間絶縁膜ILを順に形成し、その層間絶縁膜ILをCMPにより研磨する。サリサイドブロック膜SABは、下層から順に酸化シリコンを主体とする絶縁膜である保護酸化膜t1と、窒化シリコンを主体とする絶縁膜である保護窒化膜t2とによって形成する。また、層間絶縁膜ILの研磨は、高耐圧ゲートG1上面のサリサイドブロック膜SABに達するまで研磨する。

(もっと読む)

半導体装置

【課題】外部からの電気的な干渉が十分に低減されるとともに、所望の特性を発揮する容量素子が形成される半導体装置、を提供する。

【解決手段】半導体装置は、主表面1aを含む半導体基板1と、主表面1a上に規定された容量形成領域22に形成され、所定の方向に延在する複数の配線11と、容量形成領域22の周縁に配置された配線11pに隣り合い、所定の方向に延在し、電位固定された複数の配線12と、主表面1a上に形成され、複数の配線11の各々の間と、隣り合う配線11および配線12の間とを充填する絶縁体層5とを備える。複数の配線11および12は、主表面1aに平行な平面21内においてほぼ等しい間隔を隔てて配置され、かつ所定の方向に対してほぼ直角方向に並んで配置されている。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極部のしきい値電圧の変動が抑制される半導体装置と、その製造方法を提供する。

【解決手段】素子形成領域2では、P−HK膜6と、仕事関数制御用の金属膜8が形成されている。素子形成領域3では、N−HK膜7と、仕事関数制御用の金属膜9が形成されている。その金属膜8,9の上にポリシリコン膜10およびニッケルシリサイド膜11が形成されている。境界側壁絶縁膜5は、P−HK膜7とN−HK膜6とに接触する態様でP−HK膜7とN−HK膜6との間に介在するとともに、金属膜8と金属膜9とに接触する態様で金属膜8と金属膜9との間に介在している。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置における信頼性の向上を図る。

【解決手段】下段側の第1半導体パッケージ7上に上段側の第2半導体パッケージが積層されて成るPOP型半導体装置において、第1半導体パッケージ7の第1配線基板2の複数の主面側ランド2eを、主面2aの中央部に位置するチップ搭載領域を境にその両側に振り分けて配置しているため、スルーモールド方式を採用することができる。これにより、下段側の第1半導体パッケージ7の第1配線基板2の主面2a上に形成された第1封止体4が、第1配線基板2の一方の第2辺2nの中央部から他方の第2辺2nの中央部に向かって形成されるため、下段側の第1配線基板2の反りに対する強度を高めることができ、前記POP型半導体装置の信頼性の向上を図れる。

(もっと読む)

半導体装置

【課題】非絶縁型DC−DCコンバータの小型化及び電圧変換効率を向上させる。

【解決手段】ハイサイドスイッチ用のパワーMOS・FETとローサイドスイッチ用のパワーMOS・FETとが直列に接続された回路を有する非絶縁型DC−DCコンバータにおいて、ハイサイドスイッチ用のパワートランジスタとローサイドスイッチ用のパワートランジスタと、これらを駆動するドライバ回路とを夫々異なる半導体チップ5a、5b、5cで構成し、前記3つの半導体チップ5a、5b、5cを一つのパッケージ6aに収納し、かつ、前記ハイサイドスイッチ用のパワートランジスタを含む半導体チップ5aと前記ドライバ回路を含む半導体チップ5cとを近接して配置する。

(もっと読む)

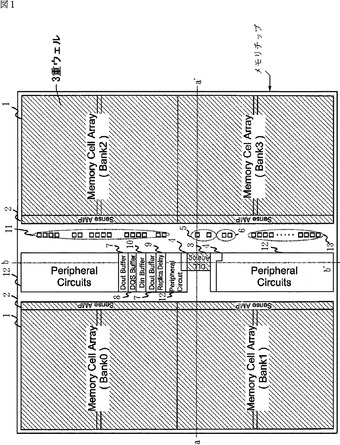

ダイナミック型半導体記憶装置

【課題】安定したクロック発生動作、高精度で低消費電力を実現しDLLを備える。

【解決手段】内部クロック信号を生成するDLL回路、内部クロック信号で動作を制御される周辺回路とメモリセルアレイを含む。第1電源電圧を供給するために同期回路に接続された第1電源パッド、第1電源電圧より低い第2電源電圧を供給するために同期回路に接続された第2電源パッド、周辺回路とメモリセルアレイに第3電源電圧を供給するための第3電源パッド、周辺回路とメモリバンクに第3電源電圧より低い第4電源電圧を供給する第4電源パッドを含む。複数のメモリセルアレイは第1領域と第2領域に分割して配置される。複数の周辺回路は第1領域と第2領域の間の第3領域に配置される。第1、2、3,4電源パッドは第1領域と前記第3領域の間の第4領域に配置されている。

【選択図】図1  (もっと読む)

(もっと読む)

41 - 50 / 4,790

[ Back to top ]