株式会社ルネサステクノロジにより出願された特許

61 - 70 / 4,790

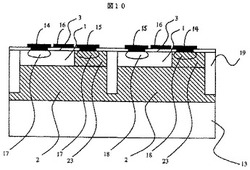

半導体装置の製造方法

【課題】Siおよびこれと同族元素であるGe,Cなどの組合せを用いて、低消費電力で高速なMOSFETを有する半導体装置の製造方法を提供する。

【解決手段】Si層1と、その上に形成されたMOSFETのゲート電極16と、Si層1に形成されたソース領域14及びドレイン領域15と、それらの間の領域に形成されるチャネル領域とを有する半導体装置の製造方法において、ソース領域14またはドレイン領域15が形成される領域のSi層1を選択的にエッチングし、形成された溝内にSiGeを選択成長させる。

(もっと読む)

半導体装置の製造方法

【課題】半導体チップのバンプ電極と、配線基板のボンディングリードとの接合部における破断を抑制する。

【解決手段】マトリクス基板(配線基板)11をピックアップして保持する基板保持部TRa、基板保持部TRaを支持する支持部TRb、支持部TRbとともにマトリクス基板11を搬送する搬送部TRc、およびマトリクス基板11を加熱するヒータ(基板加熱部)TRdを有する搬送装置TRを用いて、半導体チップ1の複数の突起電極とボンディングリードとが電気的に接続されたマトリクス基板11を、加熱されたアンダフィル樹脂充填ステージ(第2ステージ)に搬送する。

(もっと読む)

磁気記憶装置

【課題】書き込み特性の安定した磁気記憶装置を提供する。

【解決手段】第1非磁性膜2は記録層3上に設けられている。第1強磁性膜1dは、第1非磁性膜2上に設けられ、かつ第1の磁化M1dおよび第1の膜厚t1dを有する。第2非磁性膜1cは第1強磁性膜1d上に設けられている。第2強磁性膜1bは、第2非磁性膜1c上に設けられ、かつ第1強磁性膜1dと反平行結合し、かつ第2の磁化M1bおよび第2の膜厚t1bを有する。反強磁性膜1aは第2強磁性膜1b上に設けられている。第1の磁化M1dおよび第1の膜厚t1dの積と第2の磁化M1bおよび第2の膜厚t1bの積との和は、記録層の磁化M3aと記録層の膜厚t3aとの積よりも小さい。

(もっと読む)

表示装置駆動回路及び表示装置

【課題】圧縮率を大きくしても画質劣化が大きくない表示画像の場合は、圧縮率を高くして消費電力を削減でき、また圧縮率を大きくすると画質劣化が大きい表示画像の場合は圧縮率を低くし、データ伸張後の十分な画質を確保する。

【解決手段】表示装置駆動回路(101)は、表示データ圧縮回路(109)、記録回路(110)、表示データ伸張回路(111)、出力回路(112,113)を備える。上記表示装置駆動回路には、圧縮率設定回路(107)を設け、上記表示データ圧縮回路には、上記圧縮率設定回路に設定された圧縮率に従って上記表示データを圧縮する機能を含める。これにより、圧縮率を大きくしても画質劣化が大きくない表示画像の場合は、圧縮率を高くして消費電力を削減できる。また圧縮率を大きくすると画質劣化が大きい表示画像の場合は圧縮率を低くし、データ伸張後の十分な画質を確保することができる。

(もっと読む)

半導体装置

【課題】排他処理に伴って抑止されるべきアクセス要求を調停前に排除することができ、調停によって受理されるべきアクセス要求を早く確定することができる半導体装置を提供する。

【解決手段】排他的アクセスの対象となるアドレス情報などを排他情報バッファ(81)に保持し、イニシエータ(60,61,62)が出力するアドレス情報と前記保持されたアドレス情報を比較する。これにより、排他的アクセスの対象であるアドレスを対象とするピンポイントの排他処理を実現する。調停処理に先立って排他処理に伴うアクセス要求の排除を行う。このため、排他処理に伴って抑止されるべきアクセス要求が調停処理されることを防止し、イニシエータがアクセス要求を行ってからアクセス要求が受理されるまでの時間を短くすることが出来る。

(もっと読む)

半導体集積回路装置

【課題】スタンダードセルを小型化することのできる技術を提供する。

【解決手段】電源電位Vddを供給し、第1方向に沿って形成された第1タップと、電源電位Vssを供給し、第1方向と交差する第2方向に第1タップと対向して配置され、第1方向に沿って形成された第2タップと、第1タップと第2タップとの間に形成されたスタンダードセル3において、第2方向における第1タップの中心と第2方向における第2タップの中心との間のセルの高さ(距離L)を[(整数+0.5)×第2層目の配線の配線ピッチ]または[(整数+0.25)×第2層目の配線の配線ピッチ]とする。

(もっと読む)

半導体集積回路

【課題】電源電圧の変化に依存する内蔵フィルタの周波数特性の不所望な変化を軽減すること。

【解決手段】半導体集積回路は校正回路200を具備し、内蔵容量70:151は容量とスイッチを有する。V・I変換器30、20は基準電圧を電流に変換して、電流に応答する時間積分器40、50は容量70の時間積分を実行して、電圧比較器80は基準電圧と内蔵容量70の端子電圧を比較する。校正動作の間に時間積分と電圧比較が実行され、その結果はラッチ90に格納される。校正動作の完了時のラッチ90の格納結果に従って、内蔵フィルタ150の周波数特性が決定される。V・I変換器30、20のスイッチ素子SW0のNチャンネルMOSトランジスタのゲートに、校正動作の間に安定化電圧VREFが供給される。

(もっと読む)

半導体集積回路装置およびそれを用いた非接触/接触電子装置ならびに携帯情報端末

【課題】接触型動作モードと非接触型動作モードを有して、安定した電源電圧を内部回路に供給すること。

【解決手段】半導体集積回路装置U2は、アンテナ端子LA、LB、整流回路B1、電源電圧端子VDD、シャントレギュレータ回路B2、シリーズレギュレータ回路B3を具備する。内部電源ラインVDDAの電圧が第1設定電圧V1以上に上昇した際には、シャントレギュレータ回路B2はプルダウントランジスタM1にプルダウン電流I1を流す。内部電源ラインVDDAの電圧が第2設定電圧V2以下に低下した際には、シリーズレギュレータ回路B3はプルアップトランジスタM2にプルアップ電流I2を流す。第1設定電圧V1のレベルは、第2設定電圧V2のレベルよりも高いレベルに設定される。2つのレギュレータ回路B2、B3の動作の競合が、防止される。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】半導体集積回路装置の集積度の向上を図ることのできる技術を提供する。

【解決手段】セルの高さ方向に隣接して配置されるセルrow上段の2入力NAND回路6とセルrow下段のインバータ回路1との間の結線に、2層目以上の配線を用いずに、1層目の配線M1よりも下層に位置し、2入力NAND回路6またはインバータ回路1を構成するMISFETのゲート電極7N2,7P2と一体化した導電体膜からなる配線8を用いる。

(もっと読む)

半導体装置およびその製造方法

【課題】ボラジン系化合物の絶縁膜を用いて、絶縁材料と配線材料との間の密着性や、機械強度等の特性が向上された半導体装置およびその製造方法を提供する。

【解決手段】凹部に第1の導体層が埋め込まれた第1の絶縁層と、第1の絶縁層上に形成されたエッチングストッパー層と、エッチングストッパー層上に形成された第2の絶縁層と、第2の絶縁層上に形成された第3の絶縁層と、第2の絶縁層と第3の絶縁層との凹部に埋め込まれた第2の導体層と、を含む半導体装置であって、第2の絶縁層および第3の絶縁層は、炭素含有ボラジン化合物を原料として化学的気相反応成長法によって形成され、第3の絶縁層の炭素含有率が、第2の絶縁層の炭素含有率よりも小さく、第2の導体層の外周に、金属材料で構成された導体拡散防止層が形成されている半導体装置である。

(もっと読む)

61 - 70 / 4,790

[ Back to top ]