株式会社ルネサステクノロジにより出願された特許

81 - 90 / 4,790

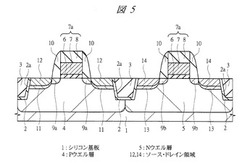

半導体装置およびその製造方法

【課題】CMISのソース・ドレイン領域端部における転位の発生および拡散抵抗の上昇を防止する。

【解決手段】CMISにおけるソース・ドレイン領域12、14の形成時、シリコン基板1に不純物をイオン注入する前に、Pウエル層4には転位抑制元素としてアルゴンを打ち込み、かつNウエル層5には窒素を転位抑制元素として打ち込む。これにより転位の発生を抑制しつつ、かつ、Pウエル層4とNウエル層5それぞれに適した転移抑制元素を打ち分けることで拡散抵抗の上昇を抑制し、歩留まりを向上させ、素子の信頼性を高めることができる。

(もっと読む)

半導体装置

【課題】高電位側スイッチ素子の十分な駆動電圧を実現した半導体装置を提供する。

【解決手段】スイッチPMOSは、低電位側の出力MOSがオンのときにオンとなり、ブートストラップ容量(以下、容量という)を電源電圧に充電し、この出力MOSがオフのときにオフとなり、オンとなる高電圧側出力MOSを通した入力電圧と容量に蓄積された電圧が加算されて昇圧電圧が形成される。スイッチPMOSのソース領域およびドレイン領域は、逆の導電型を有するウェル領域内に形成される。容量で形成された昇圧電圧が電源電圧より高くなった時に、一方のソース領域またはドレイン領域とウェル領域によって形成される寄生ダイオードに対し逆方向電圧が印加されるように、スイッチPMOSの一方のソース領域またはドレイン領域およびウェル領域が容量の昇圧電圧側に接続されている。

(もっと読む)

電源領域分割仕様探索プログラムおよび電源領域分割仕様探索システム

【課題】半導体チップにおける電源領域の最適な分割仕様を遺伝的アルゴリズムを利用して探索する電源領域分割仕様探索プログラムを提供する。

【解決手段】現世代の複数の分割候補毎に評価関数により評価値を算出するステップS101と、評価値が低い分割候補を淘汰するステップS102とを実行し、淘汰されなかった各分割候補については、各モジュールの移動確率を算出するステップS103と、他のグループに移動させる候補となるモジュールを決定するステップS104と、他のグループに属する各モジュールと移動候補のモジュールとの間の相関性に基づいて相関度を算出し、他のグループに対する移動先確率を算出するステップS105と、移動先となるグループを決定して移動するステップS106とを実行し、淘汰された各分割候補については、新たな分割候補を生成するステップS107を実行することによって、次世代の複数の分割候補を生成する。

(もっと読む)

RF電力増幅装置

【課題】負荷変動によってVSWR(電圧定在波比)の値が極端に大きくなった場合でも、出力電力結合器の電子部品の溶断の危険性を軽減すること。

【解決手段】RF電力増幅装置HPA_MDは、第1と第2のRF電力増幅回路PA1、PA2、ウィルキンソン・パワー・コンバイナによって構成された出力電力結合器Out_PCを具備する。出力電力結合器Out_PCの第1と第2の入力端子にRF電力増幅回路PA1、PA2のRF増幅出力信号が供給されて、出力端子OutからRF増幅出力信号が生成される。出力電力結合器Out_PCで、第1入力端子と出力端子の間のインピーダンスと、第2入力端子と出力端子の間のインピーダンスとは略等しく設定され、第1入力端子と第2入力端子の間の抵抗R61は、例えば渦電流を生成するインダクタ等のリアクタンス素子L63によって置換されている。

(もっと読む)

メモリコントローラおよびデータ処理装置

【課題】複数のメモリアクセスリクエスタからのリクエストでも、バスの使用効率を高めるためのグループ化が可能なメモリコントローラおよびデータ処理装置を提供する。

【解決手段】リクエストキュー22は、複数のメモリアクセスリクエスタから受信したリクエストを格納する。併合部31は、リクエストキュー22内のリクエストのうち、DDR2−SDRAMにおける1回の読出しサイクルまたは書込みサイクルでアクセス可能なリクエストを併合する。メモリインタフェース部27は、リクエストに従って、DDR2−SDRAMに対してアクセスを行ない、併合された複数のリクエストに対するDDR2−SDRAMのアクセスを一括して行なう。

(もっと読む)

半導体装置

【課題】先端プロセスでは、MOSのゲートトンネルリーク電流が増大し、低リーク電流での待機が必要となる半導体装置では問題となる。

【解決手段】第1と第2のP型MOSと、第1と第2のN型MOSと夫々が有する複数のCMOS構成スタティック型メモリセルと、電源線とソース線との電位差である前記複数のスタティック型メモリセルの電源電圧を制御する制御回路であって、第3のN型MOSを有する電源電圧制御回路とを具備する。第1のN型MOSのドレイン領域のうち、コンタクトを取る領域は砥素を含み、エクステンション領域は燐を含み、第2のN型MOSのドレイン領域のうち、コンタクトを取る領域は砥素を含み、エクステンション領域は燐を含み、前記第3のN型MOSのドレイン領域は、コンタクトを取る領域及びエクステンション領域に砥素を含む。

(もっと読む)

電子ビーム吸収電流解析方法及び電子ビーム吸収電流解析器

【課題】解析対象ネットに対して前段に位置する前段ネットからのEBAC反応を防止した解析ヒット率の高いEBAC解析方法及びそれに好適な装置を提供する

【解決手段】解析対象である解析対象ネット1000に対して出力用のプリアンプ3に接続された第1のプローブ針1を接触する。また、前段ネット1100または前段ネット1100の電源配線1010に設置された第2のプローブ針2を接触する。プローブ針の接触後、電子ビームを照射し解析対象ネット1000に対する。解析対象ネット1000に蓄積された電荷はプリアンプ3を介して外部に出力される一方で、前段ネット1100に蓄積された電荷は第2のプローブ針2を介して出力され前段ネットから排除される。これにより、EBAC解析時には前段ネット1100の誤表示を防ぐことができる。

(もっと読む)

半導体装置の製造方法

【課題】窒素やフッ素のドーズ量を増やしたとしても、トランジスタのしきい値電圧のばらつき増大を抑制することができる、半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法では、N型(P型)トランジスタが形成されるトランジスタ形成領域220,230を有する、半導体基板1を用意する。そして、トランジスタ形成領域220,230の半導体基板1上に、ゲート絶縁膜3(または6)を形成する。そして、ゲート絶縁膜3(または6)越しに、トランジスタ形成領域220,230の半導体基板1に対して、窒素またはフッ素を注入する。

(もっと読む)

半導体装置

【課題】半導体集積回路にDAコンバータが内蔵され、且つ、上記DAコンバータとデジタル回路とでパッドが共有される場合のアナログ電源電圧の動作範囲を改善する。

【解決手段】複数の抵抗が結合されて成るラダー抵抗回路を含むR−2R型DAコンバータ(106)と、デジタル信号の入出力を可能とするデジタル回路(601)と、上記DAコンバータの出力ポートと上記デジタル回路の入出力ポートとの間で共有されるパッド(602)とを設ける。そして、上記R−2R型DAコンバータが非アクティブ状態とされるとき、上記ラダー抵抗回路を上記R−2R型DAコンバータから切り放すためのスイッチ制御回路(20)を設け、上記DAコンバータのアナログ信号出力ポートを導電ライン(320)によって上記パッドに直結することで、アナログ電源電圧の動作範囲を拡大する。

(もっと読む)

RFID用インレット及びその製造方法

【課題】RFID用インレットにおいて入力用のバンプ電極及びGND用のバンプ電極のみの接合強度を測定する。

【解決手段】RFID用インレットの組み立てにおいて、チップ搭載領域4cの第3パターン4fが第1パターン4d及び第2パターン4eから分離されていることにより、超音波を印加してバンプ電極2を金属パターン4に接続する際に、第3パターン4fは梁となるようなパターンによって支持されていないため、超音波の振動に合わせて動く。これにより、チップ支持用のバンプ電極2cと第3パターン4fの接合力を、入力用のバンプ電極2aと第1パターン4dの接合力やGND用のバンプ電極2bと第2パターン4eの接合力に比べて弱くすることができ、バンプ電極2の接続強度検査において、入力用のバンプ電極2a及びGND用のバンプ電極2bのみの接合強度を測定することができる。

(もっと読む)

81 - 90 / 4,790

[ Back to top ]