株式会社ルネサステクノロジにより出願された特許

1 - 10 / 4,790

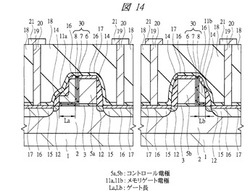

半導体装置およびその製造方法

【課題】動作速度が速く、かつ書き換え可能な回数が多くい不揮発性メモリセルと、高い信頼性を有する不揮発性メモリセルとを有する半導体装置を提供する。

【解決手段】メモリゲート電極11a、11bがコントロールゲート電極5a、5bのサイドウォール形状に形成されたスプリットゲート型の不揮発性メモリにおいて、メモリゲート長La、Lbの異なるメモリセルを同一チップ内に混載することにより、動作速度が速く書き換え可能回数の多いメモリと信頼性のあるメモリとを有するメモリチップを安価に製造することができる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】いわゆる基板品では、多層有機配線基板のデバイス搭載面上にマトリクス状にデバイス領域に半導体チップを、たとえば階段状に積層してダイ・ボンディングする。このため、ダイ・ボンダには、高精度の位置認識・位置決め機能が要求される。一方、このようなプロセスをスムースに進めるため、ダイ・ボンディング前の半導体チップの裏面には、接着剤層が設けられており、たとえば、摂氏150度前後の加熱下でダイ・ボンディングが実行されるが、基板の熱膨張による変位が、主要な位置ずれの原因となる可能性がある。

【解決手段】本願の一つの発明は、基板品のダイ・ボンディング工程において、回路基板上の2点の位置をモニタしながら、当該回路基板の半導体チップを取り付けるべき部分を加熱しながら、所定の安定した温度領域に到達したことを確認した後、半導体チップをダイ・ボンディングする半導体集積回路装置の製造方法である。

(もっと読む)

半導体装置

【課題】異なる系統の電力増幅回路を含む半導体装置を小型にする。

【解決手段】2つの周波数帯の高周波信号を取り扱うことが可能なデュアル方式のデジタル携帯電話機のRFパワーモジュールを構成する系統の異なる電力増幅回路2A,2Bを同一のICチップ1C内に配置した。この場合、電力増幅回路2A,2BをICチップ1Cの周辺に配置し、周辺回路3を電力増幅回路2A,2Bの間に配置させた。これにより、異なる系統の電力増幅回路2A,2Bを同一のICチップ1C内に設けて小型化が図れる上、異なる系統の電力増幅回路2A,2Bを同一のICチップ1Cに設けても電力増幅回路2A,2B間の距離が確保されるので電力増幅回路2A,2B間の結合を抑制させることができ、電力増幅回路2A,2B間でのクロストークを抑制できる。

(もっと読む)

ブランチング・プログラム・マシン及び並列プロセッサ

【課題】QDDを模擬する演算を実行することが可能なブランチング・プログラム・マシンを提供する。

【解決手段】命令メモリ7には、2アドレス2分岐命令、3アドレス4分岐命令、出力命令の3種の命令を少なくとも含む命令系列が記憶され、命令メモリ7はプログラムカウンタ10に設定されたアドレス情報に従って該アドレス情報で指令されるアドレスに格納された命令を命令レジスタ8に出力する。命令デコーダ9は、2アドレス2分岐命令又は3アドレス4分岐命令の場合、入力セレクタ3で入力変数を入力レジスタ4に設定し、この値に基づきジャンプ先の命令メモリ7のアドレス情報を選択しプログラムカウンタ10に設定する。また、出力命令の場合、指定される出力レジスタ5のアドレスに、指定される出力データを設定する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

半導体装置の製造方法

【課題】王水等の薬液によるシリサイド膜表面における腐食発生を抑制し、良好なPt含有シリサイド膜を形成する半導体装置の製造方法を提供する。

【解決手段】シリコンを含む半導体層を有する基板上または基板上に形成されたシリコンを含む導電膜上に、貴金属を含む金属膜を形成する工程(a)と、工程(a)の後、基板に対して熱処理を行って前記貴金属とシリコンとを反応させ、基板上または導電膜上に前記貴金属を含むシリサイド膜を形成する工程(b)と、工程(b)の後、第1の薬液を用いて、シリサイド膜のうち未反応の貴金属11の下に位置する部分上に酸化膜12を形成する工程(c)と、第2の薬液を用いて未反応の貴金属を溶解する工程(d)とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】不純物層が浅く形成された場合にも接合リーク電流の増大を抑制できるようにすると共に、コンタクトホール形成時に位置合わせずれが生じた場合にもコンタクト抵抗の上昇を抑制できるようにする。

【解決手段】基板100上に素子分離領域102及び不純物層103が互いに隣接するように形成されている。不純物層103上にシリサイド層106Bが形成されており、シリサイド層106B上に形成されたコンタクト109が形成されている。不純物層103とシリサイド層106Bとの界面は、素子分離領域102の上面よりも低く、シリサイド層106Bは素子分離領域102の上部コーナーを覆っている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の実装性の向上を図る。

【解決手段】封止部3と、半導体チップ2を支持するタブ1bと、タブ1bを支持するタブ吊りリードと、タブ1bの周囲に配置された複数のリード1aと、リードフレーム1の切断時にリード1aや前記タブ吊りリードの切断端部に形成され、かつリード1aや前記タブ吊りリードの被接続面1dから突出せずに引っ込んだ切断バリ1iと、半導体チップ2のパッドとリード1aとを接続するワイヤとからなり、リードフレーム1の切断部1kに薄肉部である凹部1jが形成されたことにより、ブレード6を用いたリード切断によって形成された切断バリ1iの先端が、リード1aや前記タブ吊りリードの被接続面1dから突出せずに引っ込んだ状態となり、これによって、リード1aや前記タブ吊りリードの被接続面1dの平坦度を向上させ、QFNの実装性の向上を図る。

(もっと読む)

半導体集積回路装置

【課題】マルチビットデルタシグマ変調器において、信号伝達関数特性が周波数依存性を持たず、量子化器入力の加算器を不要とする。

【解決手段】デルタシグマ型A/D変換器1は、入力信号Xのフィードフォワードパスとして、フィードフォワード係数kのゲインを乗じた信号とクロック信号の1周期遅延(Z-1)した入力信号に、ゲイン係数c−kを乗じた信号を加算し、積分器8の入力として加算している。この入力信号Xのフィードフォワードパスにより、積分器8は、図2に示したように、本来の積分機能と、加算器、ならびに入力信号のバッファ機能を併せ持つことができ、直接、量子化器入力に入力信号Xを加算したのと同じ効果を得ることができる。

(もっと読む)

半導体装置

【課題】樹脂6とリードフレームの界面はく離に起因したボンディングワイヤ4の断線防止と接続強度の向上を、簡単な加工で安価に製造できる装置で実現する。

【解決手段】ソースリード14上にダボ加工により突起7を設け、突起7上にボンディングワイヤ4を接続する際に超音波の減衰を防止する目的で、ソースリード14の裏側の凹部20に支柱16を設けることで、ボンディングワイヤ4とソースリード14の接続強度不足を防ぐ。また、ソースリード14とボンディングワイヤ4との接続部を取り囲むように、突起7上に連続的な段差17を設け、樹脂6とソースリード14のはく離に起因したボンディングワイヤ4の断線を防止する。

(もっと読む)

1 - 10 / 4,790

[ Back to top ]