株式会社ザイキューブにより出願された特許

31 - 36 / 36

3次元半導体集積回路装置、その製造方法、それを用いたパッケージ化3次元半導体集積回路装置及びその実装方法。

【課題】製造歩留まりの優れた3次元半導体集積回路装置及びその製造方法、それを用いたパッケージ化3次元半導体集積回路装置及びその実装方法を提供する。

【解決手段】シリコン製半導体チップをベース部に機能素子が対向するように積層し、半導体チップの材質に近いポリシリコンで半導体チップを埋め込み、あたかも1枚のウエーハの如くする。

(もっと読む)

半導体チップおよびその製造方法、ならびに半導体装置

【課題】歩留まりと信頼性の高い貫通電極を有した半導体チップおよびその製造方法を提供する。

【解決手段】この半導体チップ1は、半導体基板2を含んでいる。半導体基板2の表面には導電層3が形成されている。導電層3の下部には、半導体基板2を厚さ方向に貫通する貫通孔5が形成されている。貫通孔5内には、貫通電極8が設けられている。半導体基板2の表面には、貫通孔5を形成する前に予め、補強構造体4が、貫通孔5を完全に覆い尽くすように、貫通孔5よりも大きい径で配置されている。これにより、導電層3は、常に貫通孔5の反対面において補強構造体4で、支えられることにより、導電層3のクラックが防止される。

(もっと読む)

電子回路装置とその製造方法

【課題】 比較的簡単な製造工程によって膨大な数の配線を実装することができると共に、極めて高い歩留まりで製造することが可能な電子回路装置とその製造方法を提供し、併せてクロック信号のGHzオーダーへの高周波化に伴う高速信号伝送を実現可能な配線構造を実現する。

【解決手段】 複数の電子回路素子と、当該電子回路素子を相互接続する配線層とを有する半導体基板100と、多層配線層を内蔵する多層配線構造200とを備える。半導体基板100の前記配線層の表面と多層配線構造200の接合面とが、接続用電極を用いてあるいは接続用電極を用いずに電気的・機械的に相互接続されることによって、前記半導体基板と前記多層配線構造とが一体化されている。

(もっと読む)

半導体集積回路装置のテスト装置

【課題】3次元半導体集積回路装置に好適な半導体集積回路装置のテスト装置を提供する。

【解決手段】3次元半導体集積回路装置の、半導体回路を形成した半導体基板の動作確認用のテスト回路を仮配線で形成する。動作確認用のテスト回路は、半導体回路網の機能素子の動作検証をするときだけ機能するもので、動作検証が終了したら仮配線を除去する。仮配線は、ナノ粒子の導電性ペーストを使用して形成する。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】半導体集積回路チップダイシング工程で発生するシリコンの削りカスがチップ表面に形成したマイクロレンズ等の3次元微細構造物に付着するのを防止する手段を提供する。

【解決手段】チップ101に貫通配線106を形成して一端にマイクロバンプ107を形成してチップ信号入出力端子とし、ワイヤボンディング接続に変えて、マイクロバンプ接続手段を使う。チップ101表面に選択的にシール樹脂104を塗布して光透過板105をチップ101に固着し、チップ101表面の3次元微細構造物形成領域を密閉された常態にした後にチップ101のダイシングを行うので、シリコン削りカスは3次元微細構造物形成領域に付着しない。光透過板105表面にはシリコン削りカスが付着するが、光透過板105表面は凹凸のない平坦面なので、純水洗浄等で簡単に取り去ることができる。

(もっと読む)

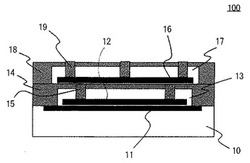

半導体集積回路装置およびその製造方法

【課題】 半導体集積回路チップに基板貫通孔を短時間に効率よく形成する。

【解決手段】 チップ表面に拡散層15を形成して配線14と接続させ、貫通孔底部の中心が拡散層15と配線14との接続部分の中心にくるようにし、且つ貫通孔底部径が配線14と拡散層15との接合部分の径と同一かそれよりもやや大きな径になるように径を制御しながら、半導体集積回路チップ裏面13よりドライエッチングを開始して、貫通孔16を形成する。本発明の半導体チップ構造では、ドライエッチングの際に使用するエッチングガスはシリコンを選択的にエッチングするガスだけでよい。従ってエッチング工程の途中でエッチングガスを他の種類のエッチングガスに交換する必要がなく、基板貫通孔を短時間に効率よく形成することができる。

(もっと読む)

31 - 36 / 36

[ Back to top ]