株式会社ザイキューブにより出願された特許

1 - 10 / 36

インターポーザを用いた積層モジュールの実装構造

【課題】 消費電力の大きい半導体デバイスを積層してなる積層モジュールであっても、それら半導体デバイスの発熱に伴う温度上昇を抑えて安定に動作させる積層モジュールの実装構造を提供する。

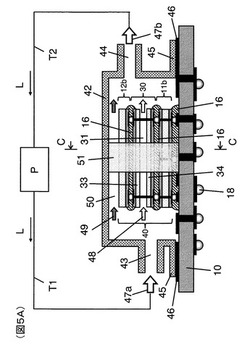

【解決手段】

基板10上に、インターポーザ30、第1半導体デバイス11b及び第2半導体デバイス12bを含む積層モジュール40と、積層モジュール40の全体を覆うカバー42とを搭載する。カバー42と基板10で形成される内部空間50を、カバー42と基板10の間に配置された堰51により、インレット43に連通する上流側空間とアウトレット44に連通する下流側空間に区分する。インターポーザ30のチャネル31により、上流側空間と下流側空間を相互に連通させる。第1半導体デバイス11b及び第2半導体デバイス12bは、チャネル31を通過する流体Lにより冷却される。

(もっと読む)

積層モジュール及びそれに用いるインターポーザ

【課題】 消費電力の大きい半導体デバイスを積層した構成を持つ場合であっても、それら半導体デバイスの発熱に伴う温度上昇を抑えて安定に動作させることができる積層モジュールを提供する。

【解決手段】

積層モジュール40bは、インターポーザ30aと、インターポーザ30aの片側に配置された1個以上の第1半導体デバイス11bと、インターポーザ30aの第1半導体デバイス11bとは反対側に配置された1個以上の第2半導体デバイス12bとを備える。インターポーザ30aは、流体が流れるチャネル31を持つ本体と、そのチャネル31を画定する本体の内壁の所定領域に配置された熱放射層61b及び熱反射層61aの少なくとも一方とを有する。

(もっと読む)

積層モジュール及びそれに用いるインターポーザ

【課題】 消費電力の大きい半導体デバイスを積層した構成を持つ場合であっても、それら半導体デバイスの発熱に伴う温度上昇を抑えて安定に動作させることができる積層モジュールを提供する。

【解決手段】

積層モジュールは、流体が流れるチャネル71を持つインターポーザ70と、インターポーザ70の片側に配置された1個以上の第1半導体デバイスと、インターポーザ70の第1半導体デバイスとは反対側に配置された1個以上の第2半導体デバイスとを備える。インターポーザ70のチャネル71は、断面積が相対的に小さい第1領域と、断面積が相対的に小大きい第2領域とを有していると共に、前記第1領域から前記第2領域へ移動する途中で流体が断熱膨張を引き起こすように構成されている。

(もっと読む)

インターポーザ及びそれを用いた半導体モジュール

【課題】 二つの熱源の間に配置した際に、それら熱源間での熱伝導をより効果的に抑制することができるインターポーザを提供する。

【解決手段】 インターポーザ24は、真空に維持されたキャビティ23を有する本体と、本体の上壁20aと下壁20bにそれぞれ形成された絶縁層22a及び22bと、絶縁層22a及び22bの上にそれぞれ形成された熱反射層21a及び21bとを備える。インターポーザ24は、その上下に搭載された半導体デバイス11aと12aの間を熱的に絶縁する。

(もっと読む)

半導体デバイス・電子部品の実装構造

【課題】 消費電力の大きい半導体デバイスや電子部品の発熱に伴う温度上昇を抑えて、安定に動作させることができる半導体デバイス・電子部品の実装構造を提供する。

【解決手段】 インターポーザ10と,インターポーザ10の表面10aに搭載された半導体デバイス11と、半導体デバイス11を包含するようにインターポーザ10の表面10aに密着・固定せしめられて、インターポーザ10と共に内部空間Sを形成するカバー12を備える。カバー12は、熱を吸収する流体Lを外部から内部空間Sに導入するインレット13と、流体Lを内部空間Sから外部に排出するアウトレット14とを有する。内部空間Sは、インレット13とアウトレット14を除いて閉じた空間である。

(もっと読む)

三次元積層構造を持つ半導体装置の製造方法

【課題】 三次元積層構造を持つ半導体装置において、積層された半導体回路層間の積層方向の電気的接続を、埋込配線を使用して容易に実現する半導体装置の製造方法を提供する。

【解決手段】 第1半導体回路層1aの半導体基板11の表面に、絶縁膜14で内壁面が覆われたトレンチ13を形成し、トレンチ13の内部に導電性材料を充填して導電性プラグ15を形成する。次に、トレンチ13とは重ならないように所望の半導体素子を基板11の表面または内部に形成し、その上に層間絶縁膜19を介して多層配線構造30を形成してから、多層配線構造30の表面にプラグ15に電気的に接続されたバンプ電極37を形成する。そして、電極37を用いて基板11を支持基板40に固定してから基板11をその裏面側から選択的に除去し、絶縁膜14を基板11の裏面側に露出させる。基板11の裏面側に露出せしめられた絶縁膜14を選択的に除去してプラグ15を露出させ、その端に電極42を形成する。

(もっと読む)

半導体チップ及びそれを搭載した半導体モジュール

【課題】半導体チップに安定した電源電流を供給したり、電源から信号系へ混入する雑音を低くするための、半導体デバイスの電源流入及び電源流出端子の端子数の低減と、前記半導体チップを搭載した実装面積の低減を可能とする半導体モジュールを提供する。

【解決手段】半導体チップ20の両面に電源系と信号系の電気的接続端子を振り分けて配置する。大電流が流れる流路の許容電流値を大きくする構成により、少ない端子数でも安定な電源供給が可能、信号系への雑音混入を低減、ピン数の低減による実装面積の低減、放熱効果の増大などが可能となる。また、この半導体チップ20を搭載した半導体モジュールにより、大電流が流れる高速動作でも安定した特性を実現できる。

(もっと読む)

半導体デバイスの実装方法

【課題】半導体デバイスを積層化した構造で、低背化が可能な手段を提供する。

【解決手段】半導体デバイス10の導電体12に複数の微小な金属塊13を形成、樹脂よりもヤング率が大きい半導体インターポーザ15の導電体17に複数の微小な金属塊18を形成しフリップチップ接続することで、導電体同士が微少な金属塊で接続されることになり低背化が達成された。また、積層化プロセスが容易になるように、前記金属塊の形状、大きさ、配置などを最適化した。

(もっと読む)

半導体チップの実装方法

【課題】高密度実装では占有面積の低減と低背化がキーとなっている。半導体デバイスを積層化した構造は高密度実装に適しているが、強度確保のための樹脂インターポーザの厚さ、上下のデバイスを電気接続する導電ボールの大きさ、ワイヤボンディングのための空間確保などにより、低背化が制限されていた。このための半導体デバイスを低背化して実装可能とする技術を提供する。

【解決手段】樹脂よりもヤング率が大きい半導体インターポーザの採用、電気接続を複数の微小な金属塊13から成る導電路20で形成、フリップチップ構成の採用などにより、低背化が達成された。また、前記金属塊の形状、大きさ、配置などを最適化することにより、積層化プロセスが容易になった。

(もっと読む)

半導体デバイスの実装方法

【課題】高密度実装では占有面積の低減と低背化がキーとなっている。半導体デバイスを積層化した構造は高密度実装に適しているが、強度確保のための樹脂インターポーザの厚さ、上下のデバイスを電気接続する導電ボールの大きさ、ワイヤボンディングのための空間確保などにより、低背化が制限されていた。

【解決手段】樹脂よりもヤング率が大きい半導体インターポーザの採用、電気接続を複数の微小な金属塊から成る導電路で形成、フリップチップ構成の採用などにより、低背化が達成された。また、前記金属塊の形状、大きさ、配置などを最適化することにより、積層化プロセスが容易になった。

(もっと読む)

1 - 10 / 36

[ Back to top ]