国立大学法人金沢大学により出願された特許

71 - 80 / 282

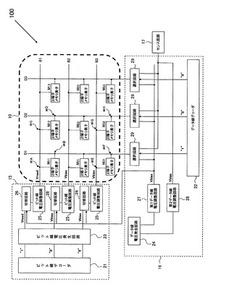

不揮発性半導体記憶装置

【課題】 リーク電流が抑制され、安定した高速メモリ動作が可能な不揮発性半導体記憶装置を提供する。

【解決手段】

不揮発性半導体記憶装置101は、ビット線の夫々につき、選択ビット線と非選択ビット線の電位をメモリ動作を行うための規定の電位に固定するビット電圧調整回路25、及び、データ線の夫々につき、選択データ線と非選択データ線の電位をメモリ動作を行うための規定の電位に固定するデータ電圧調整回路27、28を設けてなる。各電圧調整回路25、27、28は夫々,演算増幅器とトランジスタを含み、当該演算増幅器の非反転入力端子にメモリ動作に必要な電圧が入力されるとともに、当該演算増幅器の反転入力端子はビット線あるいはデータ線へ接続されることで、当該ビット線あるいはデータ線の電位は当該演算増幅器の非反転入力端子の電位に固定される。

(もっと読む)

充電回路および充電方法

【課題】電圧が変動する電源からキャパシタを充電する充電回路および充電方法を提供する。

【解決手段】第1のスイッチ、ダイオード、インダクタL、キャパシタC、キャパシタCLの端子電圧に応じて第1のスイッチのON/OFFを制御する制御手段を含むDC−DCコンバータを備え、電圧が変動する電源からキャパシタCLの端子に印加する充電電圧を生成する充電回路において、制御手段は、電源の電圧およびキャパシタCLの端子電圧に応じて、第1のスイッチのON/OFF比を制御し、電源の電圧を昇圧または降圧させて時間とともに階段状に上昇するキャパシタCLの充電電圧を生成する構成である。

(もっと読む)

不揮発性記憶素子及びその制御方法

【課題】故障率及び消費電力を充分に小さくすることができる不揮発性記憶素子を提供する。

【解決手段】複数のメモリセルが配列された不揮発性記憶素子100であって、複数のメモリセルのそれぞれは、端子Aと端子Bとを有するインバータ部と、端子Aとビット線140との導通及び非導通を切り替える選択トランジスタ120と、端子Bとビット線141との導通及び非導通を切り替える選択トランジスタ121と、一端が端子Aに接続された固定抵抗130と、固定抵抗130の他端と信号線144との導通及び非導通を切り替える制御トランジスタ122と、一端が端子Bに接続され、固定抵抗130より高抵抗又は低抵抗となることが可能な可変抵抗131と、可変抵抗131の他端と信号線144との導通及び非導通を切り替える制御トランジスタ123とを備える。

(もっと読む)

電圧生成回路

【課題】負荷容量の充放電を行わずに階段電圧および複数の定常電圧を生成することができる電圧生成回路を提供すること。

【解決手段】(N−1)個のキャパシタ(Nは2以上の整数)および各キャパシタに接続される端子1〜(N−1)と、接地電位に接続される端子0と、電源電位VDDに接続される端子Nと、接合容量と、接合容量を介して端子0と端子1、端子1と端子2、端子2と端子3、…、端子(N−1)とNの各端子間を任意の順序で周期的に接続する接続手段とを備え、端子1,2,…,(N−1)から、それぞれ定常電圧VDD/N,2VDD/N,…,(N−1)VDD/Nを取り出す構成である。

(もっと読む)

記憶回路

【課題】SRAMの1セルあたりのトランジスタ数を低減し、さらに回路構成の自由度を広げた記憶回路を提供する。

【解決手段】2つのインバータを用いて互いの出力を互いの入力とするフリップフロップと、該フリップフロップとビット線との間で信号を伝達するトランスファートランジスタとを有するメモリセルに対して、データの書き込みと読み出しを行う記憶回路において、p型の第1のMOSFETと第2のMOSFETからなり、第1のMOSFETはソースがVDDに接続され、このゲートに複数のメモリセルのトランスファートランジスタからの読み出し信号を共通に入力し、このドレインとビット線とを第2のMOSFETを介して接続する読み出し回路を備え、データの読み出し時にビット線を予め所定の電圧にプリチャージしておき、第2のMOSFETをONとしたときのビット線の電圧上昇をセンスアンプで検出することによりデータを読み出す構成である。

(もっと読む)

アセチルコリン受容体クラスター形成阻害剤

【課題】新規なイオンチャンネル阻害剤及び神経伝達過敏症の治療剤を提供することである。

【解決手段】アセチルコリン受容体のクラスター形成を阻害する化合物がイオンチャンネル阻害剤の有効成分となることを新規に見出し、本発明を完成した。

(もっと読む)

赤かび病抵抗性植物の作製方法およびその利用

【課題】トリコテセン系カビ毒を産生する糸状菌Fusarium graminearumの感染により、イネ科植物に起こる赤かび病に対して、抵抗性を有する植物の作製方法を提供する。

【解決手段】イネ科植物において、特定のアミノ酸配列を有し、赤かび病に対する感受性に関与するタンパク質をコードする遺伝子の発現を抑制する、RNAi法、アンチセンス法、遺伝子破壊法および共抑制法等の工程を含む、赤かび病抵抗性植物の作製方法。

(もっと読む)

心筋障害の検査方法

【課題】心筋障害の治療法としては、対症的な治療法で乗り切るしかない現状を鑑み、心筋障害の根本的治療を導入する足がかりとなる検査方法を提供する。

【解決手段】本発明者らは、心筋障害と自己抗体の関係に着目し、鋭意研究を重ねた結果、抗心筋型ジヒドロピリジン受容体抗体および/または抗心筋型リアノジン受容体抗体を指標とする心筋障害の検査方法を完成した。

(もっと読む)

アセチルコリン受容体クラスター形成阻害活性を有するアグリンを特異的に認識する抗体並びに該抗体を含むアセチルコリン受容体クラスター形成能促進剤及び該抗体を充填したアセチルコリン受容体クラスター形成能を阻害するアグリン除去カラム

【課題】アセチルコリン受容体のクラスター形成能の障害により生じる病気の治療剤の開発を解決すべき課題とした。

【解決手段】アセチルコリン受容体クラスター形成能を阻害する機能を持つアグリンのスプライシング・バリアントが存在することを新規に見出した。

上記知見に基づいて、アセチルコリン受容体クラスター形成阻害活性を持つアグリンを特異的に認識する抗体が、アセチルコリン受容体クラスター形成能促進剤及びアセチルコリン受容体クラスター形成阻害活性を持つアグリン除去カラムに使用できることを見出した。

(もっと読む)

半導体メモリ

【課題】Al-rich Al2O3の電荷蓄積層において、Alの組成の関数として電荷蓄積密度を解析し、電荷蓄積密度が最大となるような半導体メモリを提供する。

【解決手段】半導体基板の上面に順次、トンネル障壁層、電荷蓄積層、ブロック障壁層、ゲート電極を積層し、電荷蓄積層の局在準位に電子を蓄積することによりトランジスタのしきい値電圧を変化させる半導体メモリにおいて、電荷蓄積層をアルミニウム過剰の酸化アルミニウム(Al-rich Al2O3)とし、そのアルミニウムの組成を所定の範囲に設定し、電荷蓄積層の電荷蓄積密度が最大値(極大値)を含む所定値以上になる構成とした。

(もっと読む)

71 - 80 / 282

[ Back to top ]