フリースケール セミコンダクター インコーポレイテッドにより出願された特許

101 - 110 / 806

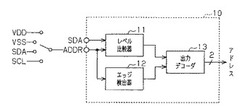

アドレスデコーダ及びアドレス設定方法

【課題】バスに接続されるモジュールのアドレスを簡易かつ効率的に設定するためのアドレスデコーダ及びアドレス設定方法を提供する。

【解決手段】アドレスデコーダ10は、レベル比較器11、エッジ検出器12、出力デコーダ13を備えている。レベル比較器11は、SDA端子に入力されたSDA信号とADDR端子に入力されたアドレス選択信号とを比較し、比較結果を出力する。ここで、両者が一致している場合には、すべてのスレーブアドレスを受信するまで比較を続ける。一致していない場合は以降の比較は行なわない。エッジ検出器12は、ADDR端子に入力されたアドレス選択信号のエッジを検出する。出力デコーダ13は、ADDR端子の接続先に応じたアドレスを設定することにより、アドレスデコーダ10に接続されたスレーブモジュールのアドレスを決定する。

(もっと読む)

SIMDオペレーションを実行するデータ処理システム及び方法

【課題】様々なロード及び格納命令を用いて、多重ベクトル・エレメントをレジスタ・ファイル内のレジスタとメモリとの間で転送する。

【解決手段】オペランド及びデータ・エレメントを格納するメモリと、少なくとも1つの汎用レジスタと、少なくとも第1の命令、及び、第1の命令に続く第2の命令を実行するプロセッサ回路と、を備え、第1の命令によって、少なくとも1つの汎用レジスタにおいてキューされるべき、メモリからのデータ・エレメントのストリームの転送を開始し、第2の命令が、少なくとも第1のソース・オペランドを含み、少なくとも1つの汎用レジスタが、第2の命令のソース・オペランドとして現れることに基づいて、プロセッサ回路が、条件付きで、メモリから、データ・エレメントのストリームの次の部分を、少なくとも1つの汎用レジスタの中にロードする、データ処理システム。

(もっと読む)

自動調整発振器

【課題】チャージポンプを用いずに、出力周波数の精度を高くすることのできる自動調整発振器を提供する。

【解決手段】発振器10は、発振回路11、パルスカウンタ12、充電回路13、リセット回路14、調整回路15及びタイミング制御部を備えている。タイミング制御部から供給されたカウント開始信号に基づいてパルスカウンタ12は、発振回路11から出力される周波数f0のパルス信号をカウントし、この間、出力信号S1を充電回路13に供給する。充電回路13は、出力信号S1が供給されている間、定電流減PS1とコンデンサC1とを接続し、接続ノードND1の電圧V1を上昇させる。調整回路15は、出力信号S1の出力が終了した場合の電圧V1が、高電位基準電圧VHより高い場合には、周波数f0を高くする調整値を発振回路11に供給し、低電位基準電圧VLより低い場合には、周波数f0を低くする調整値を発振回路11に供給する。

(もっと読む)

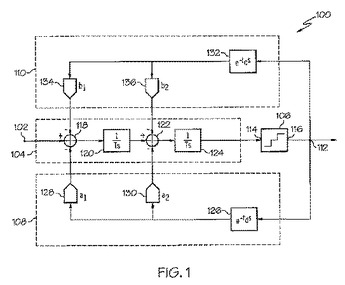

独立した遅延を有する複数のフィードバック経路を有する連続時間型シグマデルタ変調器

連続時間型シグマデルタ変調器の装置を提供する。シグマデルタ変調器(100、200、300)は、アナログ信号をデジタル値に変換するように構成された量子化器(106、206、306)を備える。主フィードバック構成(108、208、308)は量子化器に接続されており、デジタル値を第1遅延期間だけ遅延させ、この遅延値に基づき主フィードバック信号を生成する。補償フィードバック構成(110、210、310)は量子化器に接続されており、デジタル値を第2遅延期間だけ遅延させ、この遅延値に基づき補償フィードバック信号を生成する。フォワード信号構成(104、204、304)は、入力信号、主フィードバック信号および補償フィードバック信号に基づき量子化器におけるアナログ信号を生成する。第2遅延期間は第1期間から独立しており第1期間によって影響されず、第2遅延期間は補償フィードバック信号が第1遅延期間を補償するように選択される。  (もっと読む)

(もっと読む)

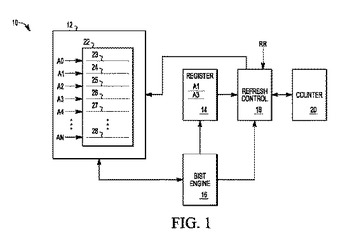

ダイナミックランダムアクセスメモリ(DRAM)リフレッシュ

ダイナミックランダムアクセスメモリ(DRAM)10をリフレッシュする方法は、第1リフレッシュレートでDRAMの少なくとも一部23にリフレッシュを実行するステップと、第2リフレッシュレートでDRAMの少なくとも第2部分24にリフレッシュを実行するステップとを含む。第2部分は、第1リフレッシュレートでデータ保持基準を満たさないDRAMの1つまたは複数の行を含み、第2リフレッシュレートは第1リフレッシュレートより高い。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】貫通ビア構造を備えた高品質な半導体装置の製造方法を提供する。

【解決手段】貫通ビアを形成する領域に窓領域を設けた酸化層パターンを備えた基板を製造する。更に、この基板を他の基板と貼り合せてSOI基板を生成する。次に、このSOI基板を研磨して薄層化する。次に、TSV構造となる領域にアイランド領域を形成する。そして、このアイランド領域の間にデバイスを形成する。更に、デバイスとTSVとを配線により接続する。次に、SOI基板の裏面のシリコン基板を削除して、裏面にアイランド領域を露出させる。そして、埋め込み酸化層に形成された窓領域を介して、TSVとのバックコンタクトを形成する。

(もっと読む)

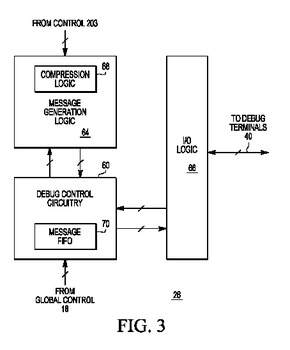

デバッグ用のアドレス変換トレースメッセージ生成

データ処理システム(10)及び方法は、外部デバッグツールをリアルタイムトレース機能を有するように許可することによってデバッグメッセージを生成する。データプロセッサ(20、22、24)は複数のデータ命令を実行し、情報記憶のためにメモリ(30)を使用する。デバッグ回路26はアドレス変換トレースメッセージを含むデバッグメッセージを生成する。仮想形態及び物理形態との間にアドレスを変換するようにアドレス変換を実行するために、メモリ管理ユニット(16)はアドレス変換論理(205)を有する。デバッグ回路(26)は、1つ以上のアドレス変換マッピングは変更される時に通信を受信するためにメモリ管理ユニット(16)に接続されるメッセージ生成回路(64)を含む。メッセージ生成回路(64)は、アドレスマッピングの変更を検出したことに応答してアドレス変換トレースメッセージを生成し、デバッグ回路(26)の外部にアドレス変換トレースメッセージを与える。  (もっと読む)

(もっと読む)

パルス幅変調回路、パルス幅変調方法及びレギュレータ

【課題】レギュレータの出力電圧を誤差電圧に対して線形的に制御できるパルス幅変調回路及びパルス幅変調方法と、出力電圧を簡単に制御可能なレギュレータとを提供する。

【解決手段】レギュレータは、パルス信号に応じてオン/オフを行なうスイッチング素子と、出力電圧と基準電圧Vrefとの差である誤差電圧Verrと基準電圧Vrefとから決定さ

れるデューティ比に応じたパルス信号をスイッチング素子に供給するPWM制御回路20とを備える。このPWM制御回路20は、誤差電圧Verrに応じた電流I1を流す電流源

21と、この電流源21とグランドとの間に設けられたキャパシタ22と、比較器25とを備える。比較器25の非反転入力端子は電流源21とキャパシタ22の接続ノードが接続され、比較器25の反転入力端子には基準電圧Vrefが印加され、比較器25の出力信

号がスイッチング素子に供給される。

(もっと読む)

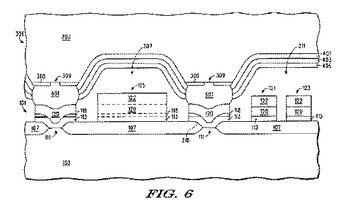

金属ゲルマニウムシリコン材料を用いた基板接合

1つの実施形態において、第1基板(103)を第2基板(303)に接合するために有用な方法は、金属含有層を前記第1基板の上に形成する工程を含む。前記金属含有層は、1つの実施形態では、微小電気機械システム(MEMS)素子とすることができる半導体素子を取り囲む。前記第2基板(303)の上には、第1シリコン含有層(401)が形成される。第2ゲルマニウム/シリコン含有層(403)は前記第1層の上に形成される。第3ゲルマニウム含有層(405)は前記第2層の上に形成される。前記第3層を前記金属含有層に接触させる。熱(及び、幾つかの実施形態では圧力)を前記第3層及び前記金属含有層に加えて、導電性の機械的接合材料を前記第1基板と前記第2基板との間に形成する。機械的接合材料でMEMSのような半導体素子を取り囲む場合、機械的接合材料は、当該材料でMEMSの気密封止を行なってMEMSを保護することができるので極めて有利である。  (もっと読む)

(もっと読む)

半導体デバイス及び半導体デバイスの製造方法

【課題】テスト回路を低耐圧の仕様にすることが可能であり、テスト回路の面積を小さくすることのできる半導体デバイス及び半導体デバイスの製造方法を提供する。

【解決手段】高電圧を用いて動作を行なう高電圧動作回路11は、パッド15,16に接続されている。高電圧動作回路11のテスト時に用いるマルチプレクサ13は、パッド15,16,17に接続されている。パッド15,16とマルチプレクサ13とを接続する配線には、それぞれヒューズ21,22が設けられている。検査ボードは、高電圧動作回路11のテスト終了後、パッド17をグランドに接続し、切断処理信号をマルチプレクサ13に供給し、パッド15(16)に電圧を印加する。切断処理信号を受信したマルチプレクサ13は、パッド15(16)とパッド17とを接続し、電流を流す。これにより、ヒューズ21(22)が切断され、マルチプレクサ13を高電圧動作回路11と絶縁状態にする。

(もっと読む)

101 - 110 / 806

[ Back to top ]