フリースケール セミコンダクター インコーポレイテッドにより出願された特許

31 - 40 / 806

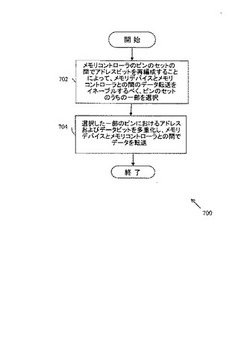

メモリコントローラアドレスおよびデータピンの多重化

【課題】メモリデバイスと通信するメモリコントローラを構成するためのシステムを提供する。

【解決手段】メモリコントローラは、複数のピンからなる第1のピンのセットを備え、各ピンはデータビットとアドレスビットとのうちの少なくとも一方に関連している。システムは、メモリコントローラの第1のピンのセットに接続されているプログラマブル論理ブロックを備える。プログラマブル論理ブロックは、第1のピンのセットの一部からなる第2のピンのセットを用い、メモリデバイスのサイズにしたがってメモリデバイスとメモリコントローラとの間のデータ転送をイネーブルする。第2のピンのセット以外のピンは、1つ以上の他のアプリケーションに利用可能である。

(もっと読む)

信頼性を改良するための導電性層間のビア

【課題】ビアの信頼性を改良するための技術を提供する。

【解決手段】別の半導体デバイスが、複数の導電性配線(12−20)を含む第1層(21)および第2層(33)を含み、複数の非機能的ビアパッド(34)が、第2層または第1層と第2層との間に含まれる。複数のダングリングビア(40)は、第1層の特定の領域内に含まれる。ダングリングビアは、第1層の1つまたは複数の配線をビアパッドの対応する一つに接続する。

(もっと読む)

固定された導電性ビアおよびその製造方法

【課題】導電性ビアおよびそれを形成する方法に関する。

【解決手段】導電性ビアが、導電性接触構造と該導電性接触構造上に配置された誘電体層の突出部との間に配置された部分を含む。1つの実施形態において、突出部は、導電性接触構造上にアンダーカット層を形成し、次に、該導電性接触構造およびアンダーカット層上に誘電体層を形成することによって形成される。誘電体層に空洞を形成し、誘電体層の突出部を形成するようにアンダーカット層の材料が該空洞を通して除去される。導電性ビアの導電性材料は次に、突出部の下および空洞に形成される。

(もっと読む)

不揮発性メモリのビットセルのI−V曲線を取得するためのデジタル方法および装置

【課題】不揮発性メモリビットセルに対する電流−電圧特性情報を生成するための方法および装置を提供する。

【解決手段】基準電流生成回路は、選択されたデジタルレジスタ設定に対応する選択された基準電流を生成する。センスアンプ回路は、遷移ゲート電圧が識別されるまで不揮発性メモリビットセルに掃引ゲート電圧が印加されるとき、前記基準電流を前記不揮発性メモリビットセルによって生成されるドレイン電流と比較する。前記遷移ゲート電圧および前記基準電流を前記不揮発性メモリビットセルに対する電流−電圧特性情報としてメモリに格納する。

(もっと読む)

不揮発性メモリにおける消去ランプパルス幅制御

【課題】消去閾値電圧分布圧縮時間を減少し、総合消去処理時間を改善するためのシステムおよび方法を提供する。

【解決手段】不揮発性メモリのメモリブロックを消去する方法が、消去パルスのパルス幅(PW)を初期幅に設定するステップ、メモリブロックが消去メトリックを満たすまで、または最大数の消去パルスが印加されるまで、メモリブロックに消去パルスを繰り返し印加するステップ(517)、消去パルスのパルス電圧の大きさを初期パルス電圧レベルから最大パルス電圧レベル(PMAX)に徐々に調整するステップ(519)、パルス電圧の大きさが初期パルス電圧レベルと最大パルス電圧レベルとの間の中間電圧レベルに達したとき、消去パルスの幅を初期幅より狭くなるように減少するステップ(525)を含む。狭いパルスはより高い電圧レベルで印加されて、メモリブロックの過剰消去の量が減少される。

(もっと読む)

半導体素子および作製方法

【課題】ソフトエラー率を有意に低下させる半導体素子およびその作製方法に関する。

【解決手段】半導体基板(100)には、第1の型の不純物でドープされた第1ウェル領域(104)の下に第1の型の第1ドープ領域(102)がある。第1ウェル領域は、第1ドープ領域と電気的に接続されている。第1ウェル領域と第1ドープ領域(102)との間に分離領域(206)を形成する。分離領域は第2ウェル領域と電気接続されている。分離領域および第2ウェル領域は、第1の不純物型と反対の型の第2の不純物型でドープされている。前記方法はさらに、第1ウェル領域内および分離領域下に第2ドープ領域を形成する工程をさらに有し得る。第1の型の不純物を有する第3ドープ領域を、分離領域の上に形成することができる。

(もっと読む)

負バイアス温度不安定性に耐性のあるラッチングセンスアンプを有するメモリおよび関連する方法

【課題】OTPメモリセルのための負バイアス温度不安定性(NBTI)耐性の高いラッチングセンスアンプを提供する。

【解決手段】集積回路は、OTPメモリセルと、第1および第2ビット線を介してメモリセルに接続されたセンスアンプ20とを備える。センスアンプは、ラッチを提供するために交差結合第1および第2インバータを備える。第1インバータは、第1ビット線に亘ってメモリセルによって提供された第1データ信号に応答する。第2インバータは、第2ビット線に亘ってメモリセルによって提供された第2データ信号に応答する。第1NBTI補償トランジスタ38は、ソース電極、ドレイン電極、および第1データ信号に応答する第1論理に接続されたゲート電極を備える。第2NBTI補償トランジスタ40は、ソース電極、ドレイン電極、および第2データ信号に応答する第2論理に接続されたゲート電極を備える。

(もっと読む)

電圧調整回路機構および関連する動作方法

【課題】従来技術の低ドロップアウト電圧調整器が所望の調整電圧を正確に維持する能力は、減少してしまう。

【解決手段】電圧調整回路の装置および関連される動作方法が提供された。例示的電圧調整回路は電圧調整構成を含み、該電圧調整構成は、入力電圧基準に基づく調整された出力電圧と、電圧調整構成の位相マージンとを増加するように構成され、電圧調整構成に接続された位相補償構成、位相補償構成に接続された検出回路を備えられる。検出回路は、閾値を満たさない出力電流を検出することに応答して、位相補償構成を無効化するように構成される。

(もっと読む)

デュアルプルーフマスを有するMEMSセンサ

【課題】熱により誘起された高ひずみおよび測定精度の低下を生じないMEMSセンサを提供する。

【解決手段】

微小電気機械システム(MEMS)センサ20は、基板26と、基板26の平坦面28に形成されたサスペンションアンカー34、36とを備える。MEMSセンサ20は、基板26上に吊らされる、第1可動素子および第2可動素子をさらに備える。可撓性部材42、44が第1可動素子38をサスペンションアンカー34に相互接続し、可撓性部材46、48が第2可動素子40をサスペンションアンカー36に相互接続する。可動素子38、40は同一の形状を有する。可動素子は矩形または入れ子構成におけるL形状可動素子108、110であってよい。可動素子38、40は、基板26における点位置94の周りに互いに回転対称に配向される。

(もっと読む)

電子ディスプレイのための時間的および空間的にオーバーラップした更新を処理するための方法および装置

【課題】ディスプレイにおいて時間的・空間的にオーバーラップした更新を処理する。

【解決手段】ディスプレイコントローラ109はフレームの各ピクセルについて動作ピクセルデータを処理し、オーバーラップ検出器413を含むピクセルプロセッサ117、衝突検出器415及び構築プロセッサ417を含む。新しい更新領域Bの任意の新しいピクセル値がフレームの現更新の領域A内にある時オーバーラップ検出器はオーバーラップを検出する。オーバーラップ領域O内の少なくとも1つのピクセルが現在の更新から与えられた終了ピクセル値GENDと異なる現更新前の開始ピクセル値GBEGを有する時及びピクセルに対する新しい更新から与えられた新しいピクセル値GNEWが終了ピクセル値と異なる時、衝突検出器が修正要求を発令する。各非オーバーラップピクセルについて新しいピクセル値を用い現更新完了前に構築プロセッサが動作ピクセルデータを更新する。

(もっと読む)

31 - 40 / 806

[ Back to top ]