大学共同利用機関法人情報・システム研究機構により出願された特許

61 - 70 / 119

分流路でのパケットペア行先アドレスに基づいて合流段を決定するデータ駆動型処理方法及び装置

【課題】パケット待ち合わせの構成を簡単化する。

【解決手段】分流路20Aの後段側のノード201〜204において合流段識別子MAを決定する。パケットペアのそれぞれの行先アドレスDAの最上位ビットからの一致ビット数をiで表すと、分流路20A上の第(i+1)段でパケットペアが分岐し、合流路40AP上の第(6−i)段でパケットペアが合流する。パケット合流段識別子を、iの値で表し、合流路40AP上の各ノードに、固定した合流段識別子の値を持たせ、これがパケットペアの合流段識別子MAと一致する場合、そのノードの処理要素でパケットペアに対する処理を行う。

(もっと読む)

データ駆動型処理装置における順序同期方法及び順序同期を行うデータ駆動型処理装置

【課題】パケット順序で同期をとることにより通常のソフトウェアにおけるオブジェクト指向の思想を導入する。

【解決手段】処理PR1の結果を処理PR2で用い又は処理PR2の結果を処理PR1で用いる場合に、ループ100を、パケット順序を維持した処理PR1のループ101Aと処理PR2のループ102Bとに分割し、これらを結合ノード103で結合し、結合ノード103で、対応するパケット同士を待ち合わせて少なくとも一方から他方へ情報を伝達することにより、処理PR1とPR2とで、少なくとも一方の処理結果を他方で利用する。

(もっと読む)

データ駆動型半導体記憶装置並びにデータ駆動型半導体記憶装置でのパケットのリード及びライト方法

【課題】ランダムアクセスを高スループットで行う。

【解決手段】メモリ10では、分流路20の下流側に、機能エレメントアレイとしてのメモリ行アレイ30を介して合流路40が接続されている。分流路20及び合流路40はいずれも6段パイプラインであり、各パイプラインステージにおけるノードは、ラッチと、転送制御回路とを備えている。メモリ行アレイ30を構成する64個のメモリ行は、互いに同一構成であり、その入力端及び出力端がそれぞれ分流路20及び合流路40の対応する出力端及入力端に結合されている。

(もっと読む)

連接パケットを使用するデータ駆動型処理方法及び装置

【課題】パケットのデータ幅を比較的狭くし、且つ、合流路における一連のパケットに他のパケットが割り込むのを防止する。

【解決手段】状態制御回路47は、フリップフロップF2が‘0’であり、ノードN1がラッチしたパケットの連接ビットCNが‘1’である場合、フリップフロップF1を‘1’にし、ノードN1がラッチしたパケットの連接ビットCNが‘0’であれば、フリップフロップF01及びF02を‘0’にし、ノードN1がラッチしたパケットの連接ビットCNが‘0’であり、ノードN1の合流段識別子がノードN1に保持されているパケットの合流段識別子MAに一致していれば、フリップフロップF1を‘0’にする。

(もっと読む)

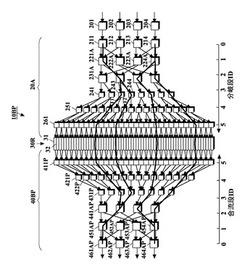

ツリー型分流路及び合流路を備えたデータ駆動型処理装置用通信路装置及びデータ駆動型処理装置用パケット転送方式

【課題】機能エレメントアレイを備えたデータ駆動型半導体装置を容易に構成する。

【解決手段】集積配置されたメモリ行アレイ30Aを介してツリー形分流路20A及びツリー形合流路40Aを配設し、メモリ行アレイ30の任意の1行に対し、行き先アドレス及び系統値を含むパケットをツリー形分流路20Aの入口ノード211〜214(系統値1〜4)のいずれかに供給し、これに対応したパケットをツリー形合流路40Aの、入口ノード211〜214に対応した出口ノード461A〜464Aから取り出す。4系統で分流路20Bの流路幅が比較的広い第4〜6段及び合流路40Bの流路幅が比較的広い第1〜4段のノードを共用する。ツリー形分流路は、複数の入口ノードのそれぞれから、系統間で合流せずに分流した位置に、次段のノードを備える構成であってもよい。

(もっと読む)

圧縮ペアパケットを分岐ノードで伸張するデータ駆動型処理方法及び装置

【課題】分流路の入口側においてパケットが混雑するのを抑制する。

【解決手段】分流路20Aの各ノードに、圧縮パケットをパケットペアに伸張する機能を備え、そのノードに、固定の分岐段識別子を割り当てておき、パケット内の合流段識別子MAの値が該ノードの分岐段識別子に一致したときに、圧縮パケットをパケットペアに伸張する。これにより、分流路20A上のパケット経路T1及びT2の分岐点で、圧縮パケットがパケットペアに伸張される。分流路20A上の分岐点は、パケットペアの行先アドレスDAの最上位ビットからの一致ビット数により定まる。一致ビット数をiで表すと、分流路20A上の第(i+1)段でパケットペアが分岐する。

(もっと読む)

有限オートマトン装置及びパターンマッチング方法

【課題】スループットを向上させると共に低消費電力化を図る。

【解決手段】データ駆動型状態テーブルメモリ120には、上位及び下位をそれぞれ状態及びデータストリーム要素とするアドレスに次状態が格納され、アドレスとデータストリーム識別子とを含むパケットが入力され、次状態とデータストリームIDとを含むパケットが出力される。合成ノード140〜143は、メモリ120の出力を入力にフィードバックさせる流路に介在され、この出力とマルチプレクサ1330〜1333の出力とを合成する。データストリームは、キュー列132の各キューに格納される。マルチプレクサ1330〜1333は、該出力に含まれるデータストリームIDに基づき、キュー列132のキューを選択して、このキューの出力段を合成ノード140〜143に結合させる。初期パケットと次状態のパケットとは、状態テーブルメモリ120と合成ノード140〜143との間の合流ノード150〜153に選択的に合流する。

(もっと読む)

データ駆動型タグテーブル装置及びデータ駆動型キャッシュメモリ並びにデータ駆動型キャッシュメモリでのリード及びライト方法

【課題】構成が比較的簡単で、連続アクセスに対しスループットを比較的高くする。

【解決手段】分流路71に供給されるパケットを、その行先アドレスに応じ順次分岐転送させて選択的にタグ行アレイ72の1つのタグ行へ供給し、キャッシュヒット/キャッシュミスヒットを判定させるとともにページアドレスを決定させ、キャッシュヒット/キャッシュミスヒットに応じ分岐ノード77で分流路20側又は入出力インターフェイス81側へ分岐転送させ、分流路20に供給されるパケットを、その行先アドレスに応じ選択的に記憶行アレイ上の1つの記憶行の一部の記憶データを読み出させてリードデータパケットを生成させ、これを、合流路40及び合流ノード82を介し入出力インターフェイス81へ転送させる。

(もっと読む)

細胞内及び細胞間の微小空間計測用カンチレバー

【課題】細胞内での安定した測定又は操作を容易に行うことが可能であり、耐久性及び信頼性のある、細胞に低侵襲な細胞内及び細胞間の微小空間計測用カンチレバーを提供する。

【解決手段】該カンチレバーは、支持部と、支持部から突出するように支持部に設けられたレバー部3と、レバー部3の自由端近傍に設けられた探針部4とを備え、細胞内及び細胞間の微小空間の計測又は操作に用いられる。探針部4は、炭素系材料からなる導電性探針7と、導電性探針7の周囲を被覆した絶縁膜8とで構成されている。

(もっと読む)

非同期式回路の制御回路

【課題】特別の休止相を設けることなく、各回路ブロックの演算終了後、初期状態に復帰することにより、高速化、低消費電力化を実現する非同期式回路の制御回路を提供する。

【解決手段】複数の回路ブロックが互いに他の回路ブロックと制御信号をやり取りすることにより一連の演算を実行する、非同期式回路において、入力制御信号が“1”から“0”に遷移したことをトリガとして演算を実施し、演算中、出力制御信号として“1”を出力し、演算が終了した後、出力制御信号を“0”に復帰するようにする。ここで、“0”とは、各回路ブロックの待機状態に対応する制御信号のステートを表したものであり、具体的な電圧等を表しているものではない。

(もっと読む)

61 - 70 / 119

[ Back to top ]