トラシット テクノロジーズにより出願された特許

1 - 5 / 5

表面層と基板とを接続するゾーンを備える部分的SOI構造を製造する方法

本発明は、表面層(20’)と、少なくとも1つの埋込み層(36、46)と、支持体(30)とを備える半導体構造を製造する方法に関し、この方法は、第1の支持体上に、第1の材料でパターン(23)を形成するステップと、前記パターン間及び前記パターン上に半導体層を形成するステップと、前記半導体層と第2の支持体(30)とを組み合わせるステップとを備える。 (もっと読む)

回路を接地面に移動する方法

本発明は半導体構造の形成方法に関し、本方法は、a)表面層(2)、前記表面層の下の埋込み層(4)、及び第1の支持体として使用される下位層(6)を備える基板の、前記表面層(2)の中又は上に、回路の少なくとも一部を形成すること、b)前記基板をハンドル基板(20)上へ移動し、第1の支持体(6)を除去すること、c)埋込み層(4)の上に導電層又は接地面形成層(14)を形成すること、d)この導電層又は接地面形成層(14)の上に結合層(12)を形成すること、及びe)このようにして得られた構造を第2の支持体(30)上に移動し、ハンドル基板(20)を除去することを含む。 (もっと読む)

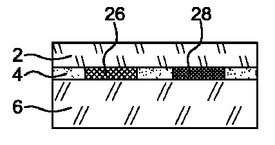

マイクロエレクトロニクス及びマイクロシステムの新規構造、及びその製造方法

本発明は、表面層(2)、少なくとも一つの埋め込み層(4)、及び支持体から構成される半導体構造体の形成方法に関する。本方法は、第一の支持体上に第一の材料からなる第一の層(44)を形成し、更に第一の層の内部に、第一の材料よりエッチング速度の大きい第二の材料からなる少なくとも一つの領域(26、28)を形成する第一のステップと、第二の支持体の上に構造体を組み立てることにより表面層(2)を形成し、二つの支持体の少なくとも一方を薄膜化する第二のステップとを含む。  (もっと読む)

(もっと読む)

ウエハの移動方法

本発明は、別の基板に移動される薄層(28)又はチップの前処理方法に関する。本方法によれば、薄層又はチップ面の表面上に、接着層(25)と呼ばれる少なくとも一つの層と、第一の境界層(22)と呼ばれる少なくとも一つの別の層を形成し、接着層は、境界層の材料に対して選択的にエッチングされる材料で構成される。

(もっと読む)

(もっと読む)

基板の準備及び組み立て方法

本発明は、材料からなる第1のウエハ(12)と第2のウエハ(14)の組み立て方法に関し、本方法は、少なくとも第1のウエハ(12)を掘削する工程、及び第1ウエハと第2ウエハを組み立てる工程を含む。

(もっと読む)

(もっと読む)

1 - 5 / 5

[ Back to top ]