サンディスク コーポレイションにより出願された特許

171 - 175 / 175

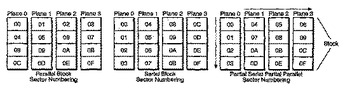

ホストの使用特性に基づいたフラッシュメモリのアドレスマッピングの適応的モード切り換え

フラッシュEEPROMなどの不揮発性メモリ記憶システムでは、性能を向上させて摩耗を低減するために、ホストのプログラミングパターンおよびコントローラのデータ整理統合パターンに応じて、コントローラは、データセクタがメモリのブロックおよびメタブロックにマップされる方法を切り換える。データは、さまざまな並列処理度でメモリにプログラムされる。  (もっと読む)

(もっと読む)

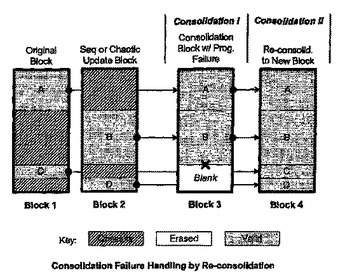

不揮発性メモリおよびフェーズ化されたプログラム障害処理を伴う方法

ブロック管理システムを伴うメモリにおいて、時間が重視されるメモリ動作中のブロック内のプログラム障害が、ブレークアウトブロック内のプログラミング動作を継続することによって処理される。後のあまり危機的でないときに、中断前に障害ブロック内に記録されたデータは他のブロックに転送され、この他のブロックもブレークアウトブロックであってもよい。その後、障害ブロックを廃棄することができる。このように、プログラミング中に不良ブロックが生じる場合に、データを失うこともなく、不良ブロック内に記憶されたデータを直ちに転送しなければならないことによって指定された時間制限を超えることもなく、不良ブロックを処理することができる。このエラー処理は、危機的な最中にすべての動作を新規のブロックに対して繰り返す必要がないようにするために、ガーベッジコレクションにとっては特に重要である。その後、都合のよいときに、不良ブロックからのデータは、他のブロックへ移転されることによって復旧される。  (もっと読む)

(もっと読む)

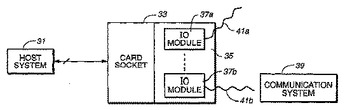

モジュール間の直接メモリアクセスを用いるマルチモジュール回路カード

取り外し可能な電子回路カード(33)は、不揮発性大容量記憶メモリを有するメモリモジュール、および分離した入出力モジュール(37a)などの複数のモジュールを有し、カードがホストシステム(31)内に挿入されているが、ホストシステムを介してデータを送信する必要のないときに、第1のモジュールを介して他のモジュールとのデータ転送を直接メモリアクセス(DMA)タイプの転送で直接に行うことができる。ホストがDMAコマンドを与えた後、カードとの直接的なこのようなデータ転送中、ホストが電力を供給し、場合によりクロック信号および他の類似の支援を供給することを除いて、データ転送はホストシステムと無関係に達成される。無線または電気接続手段のどちらかを介して転送用のデータを入出力モジュールと外部装置との間で伝達することができる。  (もっと読む)

(もっと読む)

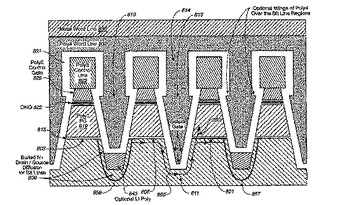

ピラー構造セルのフラッシュメモリ技術

ピラー形不揮発性メモリセル803は各々がトレンチ810によって隣接するメモリセルから絶縁されるメモリセルを各々有している。各メモリセルは基板上に処理層を積層することによって形成される。すなわち、トンネル酸化物層815、ポリシリコンフローティングゲート層819、ONOまたは酸化物層822、ポリシリコンコントロールゲート層825である。ステップの多くの態様が自己整合される。これらのメモリセルのアレイにはより少ない分割しか必要ない。さらに、このメモリセルは、電子がフローティングゲート819に対して直角またはほぼ垂直843に向けられるので、プログラミング特性が増強される。  (もっと読む)

(もっと読む)

着脱可能な電子回路カードのモジュール間の効率的な接続

複数のモジュールがカードのバスに並列に接続される着脱可能な電子回路カードを使用することによって、各モジュールがそれぞれ独立してホストとコマンドおよびデータをやり取りすることができるようにする。本発明の第1の態様によると、これは、各モジュールとホストとの対話を容易にすることができるコントローラ間インターフェイスによって実現される。第1のセットの実施形態において、これらのモジュールは単一カード上にあり、第2のセットの実施形態において、これらのモジュールは複数のカードに分散され、第1のカードはホストに装着され、他のカードはホストには直接装着されずに、第1のカードに装着される。以上のどの場合においても、ホストにはこれら複数のモジュールが単一のモジュールを搭載した単一のカードに見える。本発明のさらに別の態様において、このカードまたはカード群は、ホストと複数のプロトコルで通信可能である。  (もっと読む)

(もっと読む)

171 - 175 / 175

[ Back to top ]