サンディスク コーポレイションにより出願された特許

31 - 40 / 175

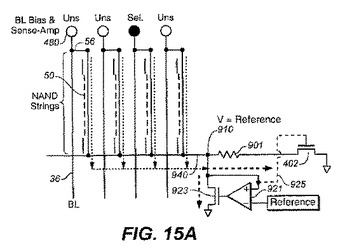

セルのソースのIR降下に対処するためのソース電位の調整

発生し得るソース線バイアスを処理するための技術が示され、不揮発性記憶装置の読み出し/書き込み回路の接地ループにおける非ゼロの抵抗によりもたらされるエラーである。エラーは、電流が流れるときのチップの接地へのソース経路の抵抗における電圧降下により引き起こされる。この目的のために、記憶装置は、ソース電位調整回路を備え、それは、基準電圧に接続された第1の入力を有すると共に集合ノードに接続可能なフィードバックループとして接続された第2の入力を有する能動的回路素子を含み、集合ノードから構造ブロックのメモリセルがセル自身の電流を接地へ流れさせる。1つの変形例は、集合ノードと接地との間に接続可能な非線形抵抗性素子を含む。  (もっと読む)

(もっと読む)

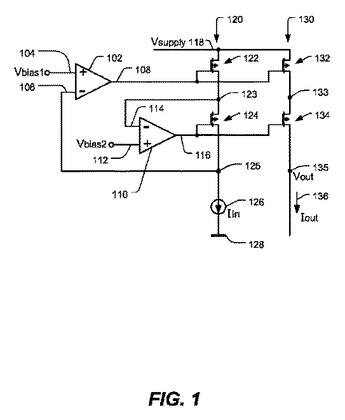

電流ミラー装置および方法

ある実施形態で、第1のトランジスタ対および第2のトランジスタ対を含む電流ミラーを備える回路が開示される。第1のトランジスタ対は第1のトランジスタおよび第2のトランジスタを含む。第2のトランジスタ対はカスコードトランジスタを含む。この回路は、第1のトランジスタおよび第2のトランジスタの両方に結合された出力を有するオペアンプも備える。  (もっと読む)

(もっと読む)

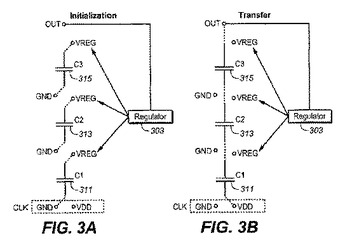

調整付き低電圧チャージポンプ

低出力電圧、高電流能力のチャージポンプを提供する技術を説明する。このチャージポンプは切替回路と複数のコンデンサを有する。初期化段階には各コンデンサの第1の極板がレギュレータ電圧を受け取るように接続され、各コンデンサの第2の極板は接地へ接続される。移動段階にはコンデンサが直列に接続され、第1のコンデンサより後ろの各コンデンサでは第2の極板が直列内の先行コンデンサの第1の極板へ接続される。ポンプの出力電圧は、直列内の最終コンデンサの第1の極板から供給される。ポンプの出力電圧レベルに応じた値を得るため、調整回路は基準電圧からレギュレータ電圧を生成する。  (もっと読む)

(もっと読む)

不揮発性メモリおよびマルチストリーム更新追跡を伴う方法

【課題】不揮発性フラッシュメモリ内のデータをプログラムする、より効率的な方法を提供する。

【解決手段】不揮発性メモリへの更新データは、所定の条件によって更新ブロックまたはスクラッチパッドブロックのいずれかといった、少なくとも2つのインターリーブするストリームに記録されてもよい。スクラッチパッドブロックを使用して、最終的には更新ブロック宛ての更新データをバッファリングする。ストリーム間の更新の記録順序についての同期情報は、ストリームのうちの少なくとも1つとともに保存される。これにより、複数のメモリブロック上に存在するであろうデータの最新書き込みバージョンを識別することができる。一実施形態において、同期情報は、第1のブロックに保存され、第2のブロック内の次の記録位置をポイントする書き込みポインタである。他の実施形態において、同期情報は、タイムスタンプである。

(もっと読む)

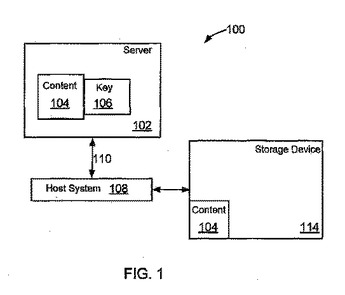

デジタルコンテンツ配布のためのシステムおよび方法

暗号化されたコンテンツをサーバから記憶装置に転送する方法およびシステムが提供される。この方法は、コンテンツを第1の鍵を用いて暗号化するステップであって、サーバがコンテンツを暗号化するステップと、ランダムセッション鍵を用いてサーバと記憶装置との間に安全な通信チャネルを確立するステップと、安全な通信チャネルを介して第1の鍵を記憶装置に送るステップと、ランダムセッション鍵を第1の鍵と取り替えるステップと、ランダムセッション鍵が第1の鍵と取り替えられた後に暗号化されたコンテンツを記憶装置に送るステップと、暗号化されたコンテンツを第1の鍵を用いて復号化するステップであって、記憶装置が暗号化されたコンテンツを復号化するステップと、記憶装置により生成された第2の鍵を用いて復号化されたコンテンツを再暗号化するステップと、再暗号化されたコンテンツを記憶装置に格納するステップとを含む。  (もっと読む)

(もっと読む)

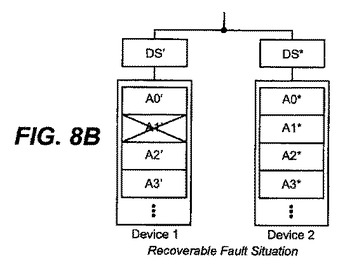

自己回復形不揮発性メモリ

不揮発性メモリアレイは2つ以上の装置を備えている。各装置が含んでいるデータはそれぞれ異なるスクランブル方式を使用してスクランブルをかけられている。同じデータが供給され、両方の装置に格納される場合には、異なるデータパターンが各装置に生じる。その結果、パターンのうちの1つがデータパターン誘導エラーを引き起こした場合に、オリジナルデータは、同じデータパターンを共有しない別のコピーから再生成させることが可能である。  (もっと読む)

(もっと読む)

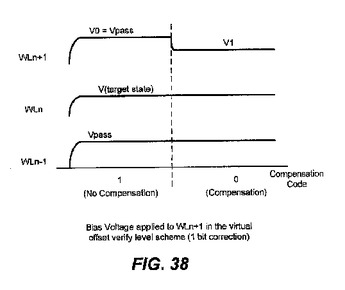

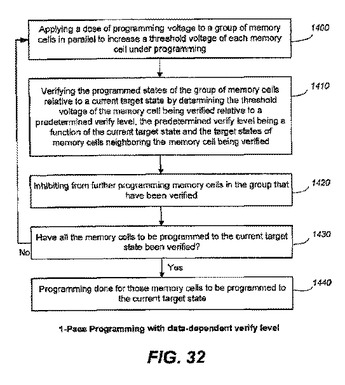

プログラミング中にベリファイするために隣接するワード線をバイアスするための不揮発性メモリおよびその方法

不揮発性メモリのための種々のプログラミング手法が、メモリセルをターゲットしきい値レベルに関してプログラムすることを含む。このプロセスは、初めにターゲットしきい値レベルより所定のオフセットだけ手前の第1のベリファイレベルに関してプログラムすることを含む。後に、プログラミングはターゲットベリファイレベルに関して完了される。第1のベリファイレベルでのベリファイについて、仮想の第1のベリファイレベルが実際上使用され、この場合、ターゲットしきい値レベルは選択されたワード線で使用され、バイアス電圧が隣接する非選択ワード線で使用される。従って、低レベルでのベリファイを避けるために、標準ベリファイレベルを実際にオフセットさせる代わりに1つ以上の隣接ワード線をバイアスすることによって、第1のプログラミングパスまたはプログラミングフェーズにおいてベリファイレベルは好ましくは仮想的にオフセットされる。  (もっと読む)

(もっと読む)

隣接するセルの摂動電荷についてプログラミング中に補償するための不揮発性メモリおよびその方法

隣接する電荷蓄積素子に蓄積された電荷に基づく電界の結合のために、不揮発性メモリの電荷蓄積素子に蓄積された見かけ上の電荷にシフトが発生する可能性がある。この結合を補償するために、所与のメモリセルのためのプログラミングプロセスは、1つ以上の隣接メモリセルのターゲットであるプログラム済み状態を考慮に入れることができる。プログラミングの量は各プログラミングパルス後にベリファイされ、プログラミングセルのための標準ベリファイレベルはターゲット状態に依存する。ベリファイレベルは、隣接するセルからの、それらのターゲット状態により確定可能な摂動の量に依存してさらに低くオフセットされる。ベリファイレベルは、実際に標準ベリファイレベルをオフセットさせる代わりに隣接ワード線をバイアスすることによって好ましくは仮想的にオフセットされる。消去済みセルをソフト−プログラムするために、両方の隣接ワード線上の隣接するセルが考慮に入れられる。  (もっと読む)

(もっと読む)

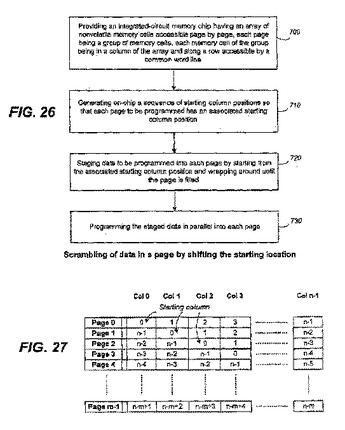

ページ内・ページ間オンチップデータ擬似ランダム化のための不揮発性メモリおよび方法

集積回路メモリチップ内の機構により、不揮発性メモリセルアレイに蓄積されるデータのスクランブリングまたはランダム化を可能にする。一実施形態において、検知中のソース負荷誤差と近傍セルのフローティングゲート間結合を抑制するため、ページ内ランダム化を役立てる。ページ単位ランダム化は、特定のデータパターンが繰り返し長期間にわたり蓄積されることから生じるプログラムディスターブ、ユーザリードディスターブ、フローティングゲート間結合を抑えるのに役立つ。別の実施形態では、ページ内ランダム化とページ単位ランダム化の両方を実施する。実施形態によってはスクランブリングまたはランダム化が予め決定されるか、あるいは符号生成擬似ランダム化となるか、あるいはユーザ主導ランダム化となる。これらの機構は、集積回路メモリチップの限られたリソースおよびバジェットの中で達成される。  (もっと読む)

(もっと読む)

不揮発性メモリのための改良された書き込み中断機構

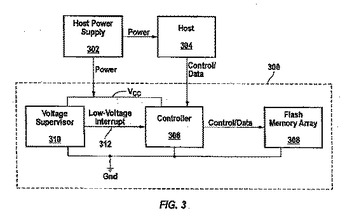

コントローラと、コントローラによって制御される不揮発性メモリアレイとを有する不揮発性メモリ(NVM)装置で、NVM装置に給電する電圧源の出力を電圧監視回路で監視する。電圧監視回路はNVM装置の一部をなす場合と、これに結合される場合とがある。電圧監視回路は、NVM装置に給電する電圧源の出力が所定値を下回るのを検出すると「低電圧」信号をアサートするように構成される。コントローラは、「低電圧」信号がディアサートされている間はメモリアレイにデータを書き込み、「低電圧」信号がアサートされている間はデータの書き込みを保留するように構成される。「低電圧」信号がアサートされると、コントローラは処理中の書き込みサイクル/プログラム操作がある場合はこれを完了し、「低電圧」信号がアサートされている間はさらなる書き込みサイクル/プログラム操作を阻止する。  (もっと読む)

(もっと読む)

31 - 40 / 175

[ Back to top ]