サンディスク コーポレイションにより出願された特許

41 - 50 / 175

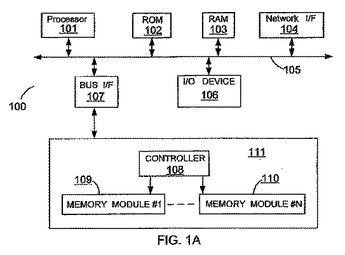

不揮発性メモリストレージ装置と通信する方法およびシステム

ストレージ装置のための方法およびシステムが提供される。一方法は、ストレージ装置のコマンド解析モジュールにより、ホストシステムからのコマンドを解釈することと、ホストシステムと連携するコマンド解析モジュールにより、操作に関する情報をコマンドから抽出することとを含む。  (もっと読む)

(もっと読む)

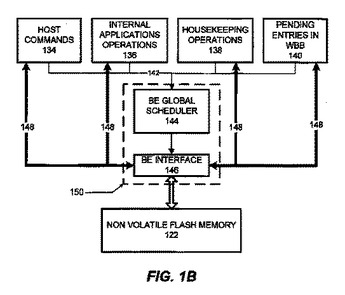

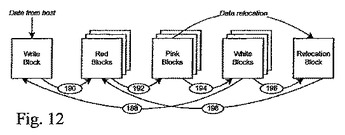

フラッシュメモリシステムにおける段階的ガーベッジコレクションおよびハウスキーピング操作

不揮発性メモリストレージシステムの一実施形態は、メモリコントローラとフラッシュメモリモジュールとを備える。メモリコントローラはフラッシュメモリモジュールの蓄積操作を管理する。メモリコントローラは、ストレージシステムへ結合されたホストから受信される1種類以上のコマンドの優先度より高い優先度を、1種類以上のハウスキーピング操作に割り当て、かつフラッシュメモリモジュールに求められる全操作を優先順位に従い処理するように構成される。  (もっと読む)

(もっと読む)

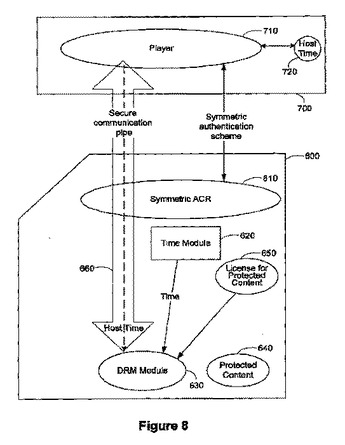

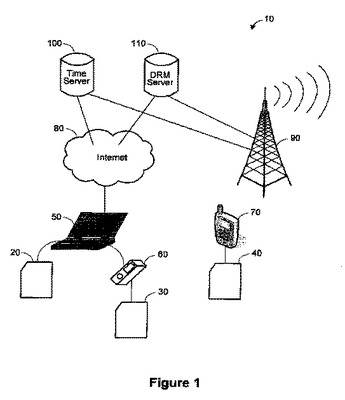

信頼されたホスト装置から時間を使用するメモリ装置とその装置で使用する方法

信頼されたホスト装置から時間を使用するメモリ装置とその装置で使用する方法とを開示する。一実施形態において、メモリ装置上のアプリケーションが、ホスト装置上で実行しメモリ装置によって認証されるエンティティから、時間本位操作の実行要求を受信する。アプリケーションは、時間本位操作の実行にあたって、メモリ装置上のタイムモジュールからの時間の代わりにホスト装置からの時間を選択し、かつ時間本位操作の実行にあたってホスト装置からの時間を使用する。他の実施形態も開示するが、それらの実施形態はそれぞれ単独で使用できるほか、組み合わせても使用できる。  (もっと読む)

(もっと読む)

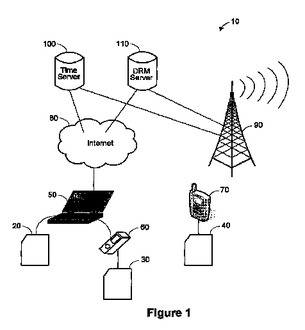

時間推定の精度を向上させるための回路を備えるメモリ装置とその装置で使用する方法

時間推定の精度を向上させるための回路を備えるメモリ装置とその装置で使用する方法を開示する。一実施形態において、メモリ装置がタイムスタンプを受信し、受信タイムスタンプを基準として稼働時間を測定する。メモリ装置は旧測定稼働時間の精度を判定し、測定稼働時間と、旧測定稼働時間の精度と、受信タイムスタンプとを用いて時間推定を生成する。別の実施形態において、測定稼働時間を調整するが、その際、時間推定を生成する場合と生成しない場合とがある。他の実施形態も開示するが、それら実施形態は単独で使用できるほか、組み合わせても使用できる。  (もっと読む)

(もっと読む)

記憶装置のためのストレージアドレス再マッピングのための方法およびシステム

ストレージアドレス再マッピングのための方法およびシステムが開示される。この方法は、クラスタのブロック内の論理アドレスを割当てることと、論理アドレスをストレージアドレス空間内に再マッピングすることとを含み、論理アドレス空間に分散させられているデータの短いランはストレージアドレス空間内のブロックの中に連続的な仕方でマッピングされる。新しいブロックの利用可能な数が所望のしきい値より低下した時には、データを受け取るために利用し得る新しいブロックを作るために、有効なデータおよび陳腐化したデータの両方を有するブロックから有効なデータがフラッシングされる。システムは、ホストファイルシステム、ホストファイルシステムとは別にホスト上に存在するかあるいは埋め込みソリッドステートディスクなどのフラッシュメモリ装置上に存在するプロセッサ実行可能な命令、または、データを論理アドレス空間からストレージアドレス空間内の完全なブロックに連続的な仕方でマッピングするように構成されているフラッシュメモリ装置のバックエンドメモリマネージャを含む。  (もっと読む)

(もっと読む)

デジタル著作権管理(DRM)ライセンス検証に用いる時間推定の精度を向上させるための回路を備えるメモリ装置とその装置で使用する方法

デジタル著作権管理(DRM)ライセンス検証に用いる時間推定の精度を向上させるための回路を備えるメモリ装置とその装置で使用する方法とを開示する。メモリ装置は、一実施形態において、メモリ装置に蓄積され、新規タイムスタンプの必要性を指定するタイムスタンプ更新方針(TUP)に対応付けられた、DRMライセンスの検証要求を受信する。メモリ装置は、DRMライセンスの検証を試みる前に、DRMライセンスに対応付けられたTUPに基づき、新規タイムスタンプが必要であるか否かを判断する。メモリ装置は、新規タイムスタンプが必要である場合に、新規タイムスタンプを受信し、その後新規タイムスタンプに基づく時間推定を用いてDRMライセンスの検証を試みる。他の実施形態も開示するが、それらの実施形態はそれぞれ単独で使用できるほか、組み合わせても使用できる。  (もっと読む)

(もっと読む)

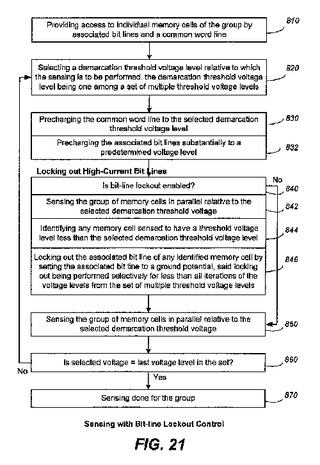

ビット線ロックアウト制御を有する検知向上のための不揮発性メモリおよび方法

多状態不揮発性メモリにおけるセル群の検知にあたって、複数の記憶状態を一通り解決するには、それぞれ異なる分界しきい値レベルを基準とする複数の検知サイクルが必要となる。それぞれの検知サイクルには検知工程がある。さらに、しきい値電圧が検知の基準となる分界しきい値レベルを下回るセルを識別するための予備検知工程またはサブサイクルを含むこともある。これらの高電流セルをオフにすることにより、節電とソースバイアスエラーの低減を達成できる。セルは、そのビット線を接地にロックアウトすることによってオフにする。その結果、検知工程を繰り返すことにより正確な結果が出る。性能を向上させ、検知操作で最大電流レベル以上消費しないようにするため、ビット線ロックアウトと予備検知を選択的にイネーブルもしくはディスエーブルする回路および方法が提供される。  (もっと読む)

(もっと読む)

エンティティの認証に用いる時間推定の精度を向上させるための回路を備えるメモリ装置とその装置で使用する方法

エンティティの認証に用いる時間推定の精度を向上させるための回路を備えるメモリ装置とその装置で使用する方法とを開示する。一実施形態において、メモリ装置がエンティティ認証要求を受信する。メモリ装置はエンティティの認証を試みる前に、新規タイムスタンプが必要であるか否かを判断する。メモリ装置は、新規タイムスタンプが必要である場合に、新規タイムスタンプを受信し、その後新規タイムスタンプに基づく時間推定を用いてエンティティの認証を試みる。メモリ装置は、別の実施形態において、新規タイムスタンプの必要性を指定する複数の異なるタイムスタンプ更新方針(TUP)を備え、新規タイムスタンプが必要であるか否かの判断は、エンティティに対応付けられたTUPに基づく。他の実施形態も開示するが、それら実施形態は単独で使用できるほか、組み合わせても使用できる。  (もっと読む)

(もっと読む)

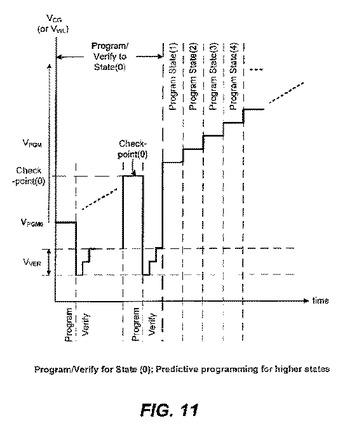

不揮発性メモリと予測プログラミングの方法

1つの範囲のしきい値電圧レベルのうちの1つにそれぞれプログラムされ得るメモリセルのアレイを有する不揮発性メモリにおいて、予測プログラミングモードが提供され、このモードにおいて、所与のメモリセルを所与の目標しきい値電圧レベルにプログラムするためにどれほどのプログラミング電圧レベルを印加する必要があるかを所定関数が予測する。このようにして、ベリファイ動作を行う必要はなく、これによりプログラム動作の性能を大幅に改善する。1つの好ましい実施形態では、所定関数は線形であり、プログラムされる各メモリセルのために1つ以上のチェックポイントにより較正される。チェックポイントは、問題のメモリセルをベリファイされる指定されたしきい値電圧レベルにプログラムする実際のプログラミング電圧である。  (もっと読む)

(もっと読む)

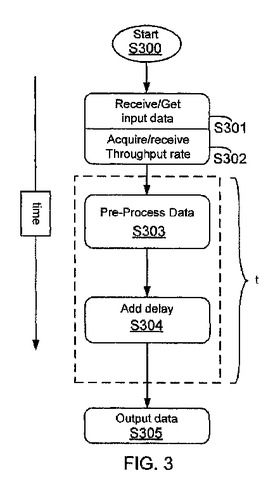

デジタルコンテンツへのアクセスを制御する方法およびシステム

アクセスシステムによるデジタルコンテンツの利用にあたってスループットレートを制御するメモリコントローラを含む蓄積システムが提供され、スループットレートには、ファイルとして蓄積されるデジタルコンテンツの関係情報が結び付けられる。また、デジタルコンテンツを利用するシステムが提供される。このシステムはデジタルコンテンツを利用するアクセスシステムを備え、アクセスシステムには、制御スループットレートでデジタルコンテンツが放出され、スループットレートには、ファイルとして蓄積されるデジタルコンテンツの関係情報が結び付けられる。  (もっと読む)

(もっと読む)

41 - 50 / 175

[ Back to top ]