サンディスク コーポレイションにより出願された特許

51 - 60 / 175

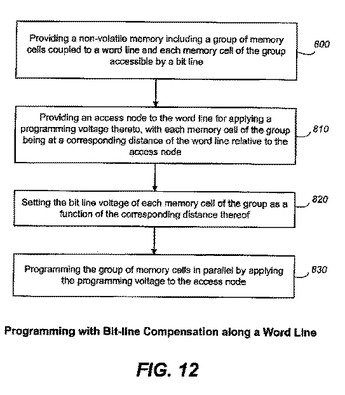

不揮発性メモリおよびワード線沿いの電圧降下を補償する方法

メモリプレーンにまたがるワード線沿いの時間定数の変化に起因するプログラミング効果の変化は、メモリプレーンにわたってビット線電圧を調整してプログラミングレートを修正することによって補償される。これにより、ワード線へ結合された1グループのメモリセルのプログラミング中にプログラミング効果の変化は大幅に低減する。その結果、メモリセルグループのプログラミングを均一に最適化でき、メモリセルグループのプログラミングに要するプログラミングパルス数は減り、性能が向上する。一実施形態において、プログラミング中にワード線電圧源に近いメモリプレーンの第1の半分に位置するビット線が第1の電圧シフタによって第1の電圧に設定され、ワード線電圧源から遠いメモリプレーンの第2の半分に位置するビット線は、第2の電圧シフタによって第2の電圧に設定される。  (もっと読む)

(もっと読む)

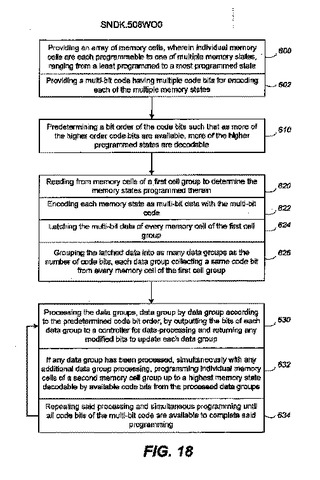

不揮発性メモリおよびキャッシュページコピー方法

不揮発性メモリおよび方法は、各メモリセルについて最小数のデータラッチを使用するキャッシュページコピーを含む。複数ビットデータは、第1のワード線に関連する群の各メモリセルから並列に読み出される。読み出されたデータは、データ処理のために所定の順序に従って群単位でメモリから送り出すための複数のデータ群に編成される。修正されたデータは、それぞれのデータ群を更新するために送り返される。所定の順序は、より多くのデータ群が処理されてプログラミングに使用可能であるほど、より多くの高くプログラムされた状態が復号可能であるようになっている。適応フルシーケンスプログラミングは、この処理と同時に実施される。このプログラミングによって、読み出されたデータは、一般に異なる消去ブロックの、好ましくは第1のワード線に隣接するワード線による摂動効果を補償されて、第2のワード線に関連する別のメモリセル群にコピーされる。  (もっと読む)

(もっと読む)

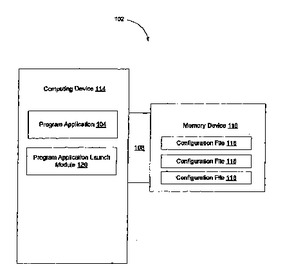

プログラムアプリケーションを起動するための方法および装置

プログラムアプリケーションを起動するための方法が提供される。ここで、コンフィギュレーション命令が記憶装置に格納され、コンフィギュレーション命令は複数のコンフィギュレーションに関連付けられる。記憶装置が計算装置に結合される時に複数のコンフィギュレーションのうちからコンフィギュレーションが選択される。その後、そのコンフィギュレーションに関連付けられているコンフィギュレーション命令が記憶装置から取り出される。プログラムアプリケーションが起動され、コンフィギュレーション命令がプログラムアプリケーションに送られる。計算装置も提供される。その計算装置はプロセッサを備える。プロセッサは、計算装置が記憶装置に結合される時に複数のコンフィギュレーションのうちからコンフィギュレーションを選択するように構成される。プロセッサは記憶装置からコンフィギュレーションに関連付けられているコンフィギュレーション命令を取り出すようにさらに構成される。さらに、プロセッサは、コンフィギュレーション命令に関連付けられているプログラムアプリケーションを起動してコンフィギュレーション命令をプログラムアプリケーションに送るように構成される。  (もっと読む)

(もっと読む)

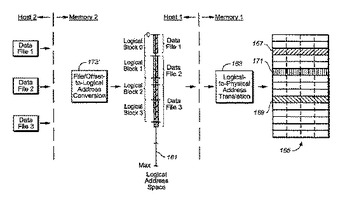

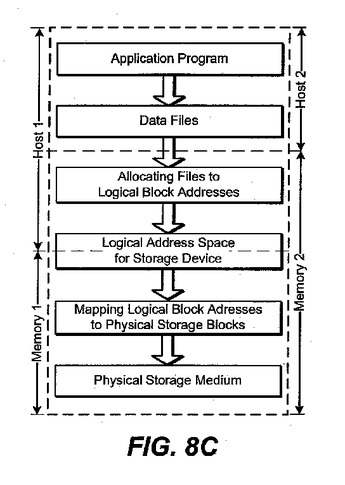

連続論理アドレス空間インターフェイスを備えるダイレクトデータファイルシステムの使用

物理メモリセルブロックを備える通常タイプのフラッシュメモリシステムの連続論理アドレス空間インターフェイス(LBAインターフェイス)の1つ以上の論理ブロックの中で、データファイルにアドレスを割り当てる。この割り当てはホスト装置で行うことができ、データファイルは通常ならばホスト装置によって生成されるが、必ずしもそうとは限らない。物理メモリブロックにおけるファイルデータの断片化の量を抑えて良好なメモリ性能を維持するため、いずれか1つのファイルのデータを収容する論理ブロックの数を規制する。ホストは、これに接続するメモリの物理的特性を学習し、これに応じてアドレス空間の論理ブロックを構成できる。  (もっと読む)

(もっと読む)

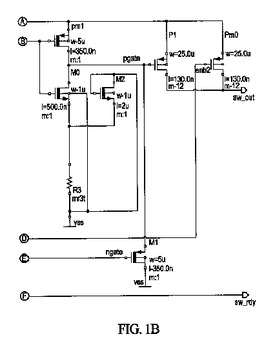

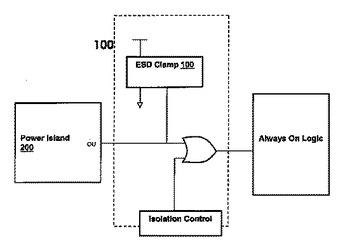

インラッシュ制限用電力アイランドを有するシステム、方法、および集積回路

電力アイランドの電源投入を管理する新しい方法は、プリチャージ段階を使用して、過渡現象および関連する電力制御ロジックの不安定性を最小限に抑えながら、アイランドの内部電源電圧を上昇させるプロセスを開始する。  (もっと読む)

(もっと読む)

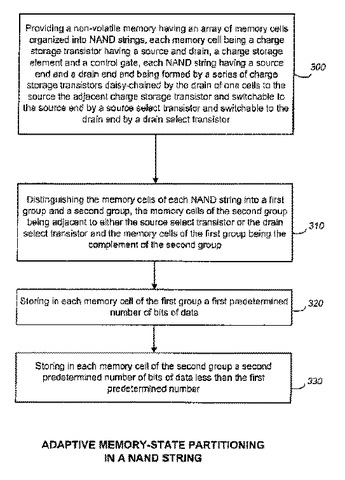

適応型メモリ状態区分を備えるNANDフラッシュメモリセルアレイおよび方法

NAND型フラッシュメモリはNANDストリングの形に構成され、それぞれのNANDストリングは一連の直列メモリセルであって、ストリング両端の選択トランジスタを通じてビット線かソース線へ接続される。NANDストリングの両端付近のメモリセルは特に、プログラムディスターブによるエラーを被りやすい。エラーを克服するため、両端付近のメモリセルを除くメモリセルは多数のビットデータを蓄積するように区分し、両端付近のメモリセルには比較的少ないビットを蓄積する、適応型メモリ状態区分方式を使用する。このようにNANDストリングの両端付近のメモリセルに比較的少ないビットを蓄積することで、エラーを克服するにあたって十分なマージンを提供する。例えば2ビットデータを蓄積するように設計されたメモリでは、2ビットデータの1ビットをNANDストリングの両端付近のセルに各々蓄積するように構成する。  (もっと読む)

(もっと読む)

ダイレクトデータファイルメモリシステムにおけるLBAインターフェイスの管理

物理メモリセルブロックを備える通常タイプのフラッシュメモリシステムの連続論理アドレス空間インターフェイス(LBAインターフェイス)の1つ以上の論理ブロックの中で、データファイルにアドレスを割り当てる。この割り当てはホスト装置で行うことができ、データファイルは通常ならばホスト装置によって生成されるが、必ずしもそうとは限らない。物理メモリブロックにおけるファイルデータの断片化の量を抑えて良好なメモリ性能を維持するため、いずれか1つのファイルのデータを収容する論理ブロックの数を規制する。ホストは、これに接続するメモリの物理的特性を学習し、これに応じてアドレス空間の論理ブロックを構成できる。  (もっと読む)

(もっと読む)

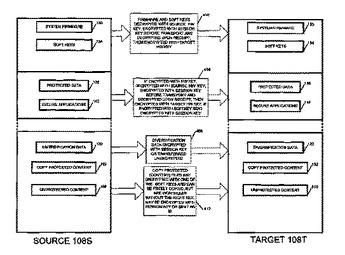

セキュアコンテンツおよびアプリケーションのコピーを防ぐセキュリティメカニズムを有するメモリカードのアップグレード

セキュアフラッシュメモリカードあるいはフラッシュドライブは、ユーザコンテンツを無許可の複写からプロテクトする。しかし、プロテクトされるユーザコンテンツであっても、1つのフラッシュカードあるいはドライブから他の1つへその正当な所有者またはライセンシーによって移すことができる。さらに、付加的な機能性をカードに付け加えるために何時でもフラッシュカードに付け加えられるセキュアファームウェアアプリケーションも、その多くは装置特有であってハードウェアの1つの特定のピースの上でだけ動作するようにも設計されているけれども、移すことができる。  (もっと読む)

(もっと読む)

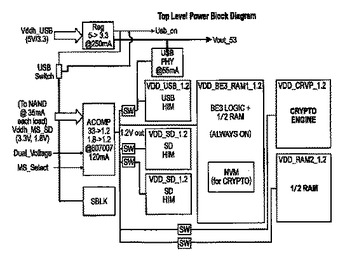

2つのタイプの減結合コンデンサを備えた集積回路および方法

デュアル電圧パワーアイランドアーキテクチャにおける最適な減結合キャパシタンスのための方法およびシステムを提供する。2つの異なるタイプの蓄積コンデンサが、チップの低電圧領域において、コンデンサが常時オン状態の領域または条件付きで起動される領域に位置するかどうかに依存して減結合に使用される。  (もっと読む)

(もっと読む)

電源アイランド境界に保護を有するシステム、回路、チップおよび方法

標準的な絶縁セルが、電源アイランド境界において、過渡電圧をクランプする保護装置をも備える集積回路を提供する。  (もっと読む)

(もっと読む)

51 - 60 / 175

[ Back to top ]