サンディスク コーポレイションにより出願された特許

1 - 10 / 175

記憶装置内のパーティションを管理する方法およびシステム

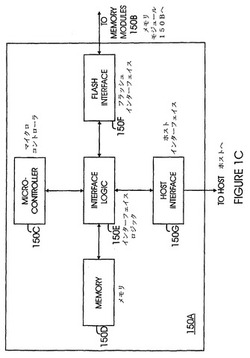

【課題】大容量記憶メモリシステムと、メモリパーティション空間を再割り当てする方法とを提供する。

【解決手段】記憶システムは、論理インターフェイスを介してホストシステムからデータを受信するようになっているマイクロプロセッサを含むメモリコントローラと、システム領域およびデータ領域を有する第1のメモリパーティションと、システム領域およびデータ領域を有する第2のメモリパーティションと、を含み、メモリコントローラは、ホストシステムにシステム領域およびデータ領域が連続しているように見えるようにシステム領域およびデータ領域の仮想ブロックアドレスを用いることにより、第2のメモリパーティションから、いっぱいであるかまたはしきい値に達した第1のメモリパーティションへメモリ空間を再割り当てする。

(もっと読む)

ページ内・ページ間オンチップデータ擬似ランダム化のための不揮発性メモリおよび方法

【課題】集積回路メモリチップ内の機構により、不揮発性メモリセルアレイに蓄積されるデータのスクランブリングまたはランダム化を可能にする。

【解決手段】一実施形態において、検知中のソース負荷誤差と近傍セルのフローティングゲート間結合を抑制するため、ページ内ランダム化を役立てる。ページ単位ランダム化は、特定のデータパターンが繰り返し長期間にわたり蓄積されることから生じるプログラムディスターブ、ユーザリードディスターブ、フローティングゲート間結合を抑えるのに役立つ。別の実施形態では、ページ内ランダム化とページ単位ランダム化の両方を実施する。実施形態によってはスクランブリングまたはランダム化が予め決定されるか、あるいは符号生成擬似ランダム化となるか、あるいはユーザ主導ランダム化となる。これらの機構は、集積回路メモリチップの限られたリソースおよびバジェットの中で達成される。

(もっと読む)

ホストと順次通信する複数の取り外し可能な不揮発性メモリ・カード

【課題】システムの初期化時にカード・アドレスをセットする速くて割合に簡単な方法を提供する。

【解決手段】データが読み書きされる2つ以上の非常に小型のカプセル入り電子回路カードは、配線で該ソケットに接続されているホスト・システムの2つ以上のソケットに取り外し可能に挿入される。コマンドおよび応答信号は、該ホストと該ソケットの全てとの間に共通に接続されている単一の回路により該ホストと該カードとの間で伝えられ、システムの初期化時には、コマンドおよび状態回路を一度に一つずつ順次各ソケットに接続することによって特有の相対カード・アドレスが該ソケットに挿入されている各カードに書込まれていると確認される。

(もっと読む)

2つのタイプの減結合コンデンサを備えた集積回路および方法

【課題】デュアル電圧パワーアイランドアーキテクチャにおいて、低いオフ状態リークを実現する事が可能な最適な減結合キャパシタンスのための方法およびシステムを提供する。

【解決手段】チップの低電圧領域において、誘電体膜厚の異なる2つの異なるタイプのコンデンサが使用される。膜厚の薄いコンデンサは常時オン状態の領域で使用され、膜厚の厚いコンデンサーは条件付きで起動される領域で使用される。これによって低いオフ状態リークをで減結合コンデンサーを使用できる。

(もっと読む)

データラン・プログラミング

【課題】ユーザデータをメモリアレイにプログラムし、またメモリアレイからユーザデータを読み出す間の並列性を高める。

【解決手段】データラン内のデータは、不揮発性メモリアレイの、データ境界の位置に応じて構成される適応メタブロック98に格納される。適応メタブロック98を形成するために使われるプレーンは、アレイの消去ブロックの効率的な使用を提供するアルゴリズムに従って選択される。また、そのプレーン内でコピー操作を実行することができるように、更新されているマテリアルのために使用されているのと同じプレーンを新しいマテリアルのために使用することを考慮する。同時に2つ以上の適応メタブロックをプログラムすることによって、小さな適応メタブロックで高い並列性を維持する。

(もっと読む)

不揮発性メモリおよび改善された部分的ページプログラミング機能を備えた制御処理

【課題】2以上のシーケンシャルなプログラミングパス時にメモリセルのプログラミングが行われるプログラミング方式において、メモリセルのうちの少なくともいくつかのメモリセルを第2のパス中にプログラムするのに不十分なホストデータしか存在しないとき、誤ったプログラミングが生じない方式を提供する。

【解決手段】プログラミング方式を変更することによって、誤ったプログラミングの防止が可能となる。第2のプログラミングパス中、誤ったしきい値電圧に合わせたプログラミングをこのメモリセルに行わせないようにするコード構成を選択することにより、エラーを含む状態に合わせたプログラミングをこのセルに行わせないようにする代替データに基づいてこのメモリセルのプログラミングを行う。

(もっと読む)

不揮発性メモリおよび制御データ管理を伴う方法

【課題】ブロック管理システムを伴う不揮発性メモリにおいて、制御データなどの重要なデータが、複製されて保持される。多状態メモリにおける重要なデータの2つのコピーをエラーに対して強いように書き込みおよび読み出す。

【解決手段】重要なデータは、複製にして保持しておけば、信頼性のレベルが上がることが保証される。メモリセルの同一のセットのマルチビットを順次にプログラムするための2パスプログラミング手法を使用する多状態メモリシステムについて、第1のパスによって確立されたデータが第2のパスにおけるいかなるプログラミングエラーによっても破損されないように、複製が行われる。また、複製は、書き込みの異常終了の検出、誤検出の検出の助けとなり、信頼性のレベルが向上する。

(もっと読む)

メモリカードコントローラファームウェアのハードウェアドライバ完全性チェック

【課題】カード上で常時実行するファームウェアの完全性および信頼性の両方を確実にする。

【解決手段】メモリシステム10のフラッシュメモリ20内に前記メモリシステム10のファームウェアを設け、前記ファームウェアを前記メモリシステム10のハードウェアで実施される暗号化エンジン40に通し、前記ファームウェアについてのハッシュ値を前記ハードウェアで実施される暗号化エンジン40で計算し、計算されたハッシュ値を記憶されたハッシュ値と比較し、前記計算されたハッシュ値が前記記憶されたハッシュ値と一致する場合に、前記ファームウェアを実行する。

(もっと読む)

フラッシュメモリセルの自動昇圧システム

【課題】NANDストリングの異なったセルのプログラミングサイクル中にワードライン0に結合されたメモリセルのしきい値電圧のシフトを減らしたり、または防止する。

【解決手段】消去された領域の自己昇圧と局部的な自己昇圧方式を含む色々な異なった自己昇圧方式のいずれかで実施される。改造された消去された領域の自己昇圧方式では、低い電圧が選択されたワードラインのソース側の2本以上のワードラインに印加され、帯域から帯域へのトンネリングを低減すると共に2つの昇圧されたチャネル領域間の絶縁を改善する。改造された局部的な自己昇圧方式では、0ボルトまたは低い電圧が選択されたワードラインのソース側の2本以上のワードラインとドレイン側の2本以上のワードラインに印加されて、帯域から帯域へのトンネリングを低減すると共に選択されたワードラインに結合されたチャネル領域の絶縁を改善する。

(もっと読む)

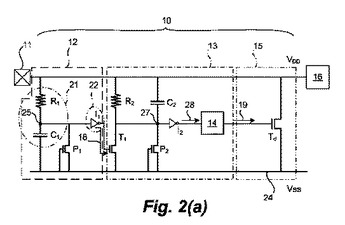

立ち上がり時間検出器および放電継続回路を有する静電放電保護回路

本発明の方法および素子は静電放電(ESD)保護回路を含む。この回路は、入力信号のスルーレートを検出することができ、かつ入力信号のスルーレートがしきい値よりも大きいかどうかを判定することができる立ち上がり時間依存活性化回路を含む。ESD事象の場合、立ち上がり時間依存活性化回路はトリガ信号を発生する。加えて、立ち上がり時間依存活性化回路は、ESD消散回路にさらに結合されるESD消散継続時間制御回路に結合される。この配置は、トリガ信号によってESD消散継続時間制御回路が活性化され、ESD消散継続時間制御回路は応答して活性化信号を生成し、活性化信号は、ESD消散回路を活性化し、ESD消散回路が活性状態のままであり続ける時間の長さを制御することを可能にする。ESD消散回路は、ESDエネルギーを被保護内部回路外へ経路変更するシャントを含む。ESD消散継続時間制御回路は、被保護回路を損傷することなくESDエネルギーを放電するのに十分な期間にわたってエネルギーの分流を保つようにさらに構成される。  (もっと読む)

(もっと読む)

1 - 10 / 175

[ Back to top ]