エステミクロエレクトロニクス(クロレ・2)・エスアーエスにより出願された特許

1 - 6 / 6

集積回路及びカプセル化されたN/MEMSを備えた装置及びその製造方法

少なくとも一つの集積回路(104)と、少なくとも一つのN/MEMS(122)とを含む装置(100)の製造方法であって、

・少なくとも基板(120)の第1の領域上に配置される少なくとも一つの上部層(116)内でのN/MEMSの製造、及び

・基板の第2の領域及び/又は少なくとも基板の第2の領域上方に配置される半導体層内での集積回路の製造、の段階を少なくとも含み、

集積回路のゲート(114)の製造に、及び/又は集積回路の少なくとも一つの電気的コンタクト(128、130、132、134)の製造に使用される少なくとも一つの層からの、N/MEMSをカプセル化するカバー(124)の製造をさらに含む、製造方法。  (もっと読む)

(もっと読む)

集積電子回路におけるワイヤー部の形成方法

集積回路にワイヤー部(101、102)を形成する方法は、シード材質の層部分(11、12)の側面上にワイヤー部をエピタキシャル成長する段階を備える。ワイヤー部の断面寸法はシード材質の層部分の厚さ及び成長段階の継続時間に対応する。その後、シード材質の層部分が選択的に除去され、ワイヤー部が回路上に固定的に保持される。その後、回路を加熱することで、ワイヤー部の断面を丸くすることができる。得られたワイヤー部の直径は、約10nmとすることができる。この方法は、ショットチャネル効果がないMOSトランジスタのチャネルを形成するのに用いられ得る。  (もっと読む)

(もっと読む)

ハフニウム酸化物に基づく薄膜部分を備えた集積電子回路

本発明は、ハフニウム酸化物に基づく薄膜(1)を含む集積電子回路に関連している。本発明によれば、前記部分は同様に、ハフニウムとマグネシウムの混合酸化物の形態においてマグネシウム原子を含有している。一つのそのような部分は高い誘電率、及び非常に低い漏れ電流を有している。本発明は特に、MOSトランジスタのゲート絶縁膜の部分、またはMIMキャパシタ誘電体の部分の形成に適している。  (もっと読む)

(もっと読む)

誘電材料における金属配線

第1の誘電材料で作製された誘電層内に、導電性部分を含む配線を含む、半導体デバイスを製造するための方法が開示される。誘電層内にトレンチが形成される。この方法は、トレンチの側壁を形成する誘電層の露出部分を除去するステップと、ライナーが第2の誘電材料で作製された、誘電ライナーをトレンチの側壁上に堆積するステップとをさらに含む。  (もっと読む)

(もっと読む)

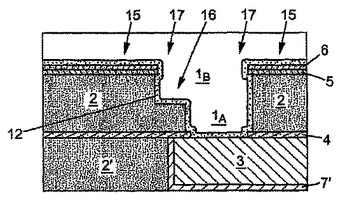

相互接続配線内における複数のエアギャップの横方向分布の制御

【課題】相互接続構造内におけるエアギャップの形成に際し、横方向の制御性を向上させること。

【解決手段】集積回路を製造するための方法であって、−集積回路をなす相互接続構造積層体(10)を形成し;−相互接続構造積層体の表面(15)上に、エアキャビティの形成を意図した規定部分(14)を規定し;−基板の表面の規定部分を取り囲む少なくとも1つのトレンチ領域を規定するとともに、トレンチ領域内において相互接続構造積層体内に少なくとも1つのトレンチ(34)を形成し;−トレンチをコーティングするようにして硬質マスク層(26)を成膜し;−除去剤(24)を使用することによって透過材料を透過させつつ犠牲材料を除去することにより、基板の表面の規定部分の下方に、少なくとも1つのエアキャビティ(32)を形成する。

(もっと読む)

電子集積回路の製造方法及びそれによって得られる電子集積回路

基板(100)上に一時的な材料の部分(1)の形成を含む集積回路の製造方法であって、その基板の一部は吸収材料からなる集積回路の製造方法である。一時的な材料は、コバルト、ニッケル、チタン、タンタル、タングステン、モリブデン、ガリウム、インジウム、銀、金、鉄及び/又はクロムを含む。硬質部分(3、4)は、吸収材料からなる基板の部分に対向する一時的な材料(1)の部分の一側で基板と接触して形成される。前記回路は、一時的な材料が吸収材料からなる基板の部分に吸収される方法で加熱される。従って、実質的に材料が無い領域(V)は、一時的な材料(1)の部分の場所に形成される。その実質的に空の領域は、キャパシタの補強材の間に位置する誘電材料に置き換わることができる。  (もっと読む)

(もっと読む)

1 - 6 / 6

[ Back to top ]