力成科技股▲分▼有限公司により出願された特許

1 - 10 / 36

マルチチップ積層体の製造方法

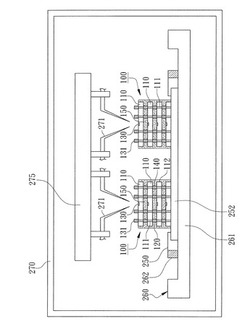

【課題】 本発明の目的は、無基板チップ積層体の導通検査を従来の検査装置で実施可能なTSV実装プロセスを用いて製造するマルチチップ積層体の製造方法を提供する。

【解決手段】 ウエハを分割して形成したチップ110の表面に複数のテスト電極130と複数の外部電極131とを形成する。チップ110には外部電極131とテスト電極130とを導通する複数のシリコン貫通孔111が設けられる。次に、無基板チップ積層体100を接着テープ252の上に固定し、充填封止体150を接着テープ252上に形成する。次に、ウエハテストトレー260内に接着テープ252を支持するテープキャリア250を固定する。導通検査では、無基板チップ積層体100は接着テープ252に接着されたままウエハ検査装置270内に搭載され、ウエハ検査装置270の複数のプローブ271によって無基板チップ積層体100の導通の良否を判定する。

(もっと読む)

フリップチップキャリア、及びこれを用いた半導体実装方法

【課題】従来のMPS−C2半導体パッケージに起きる半田材ブリッジとパッケージ反りを抑制可能なフリップチップキャリア、及びこれを用いた半導体実装方法を提供する。

【解決手段】フリップチップキャリア100は、基板110と複数の独立パッドマスク120とを含む。基板110は、上表面111、および、上表面111に設置される複数のパッド112を有する。独立パッドマスク120は、パッド112を覆う。各独立パッドマスク120は、対応するパッド112と貼り付ける感光性粘着層121、及び感光性粘着層121上に形成される透光性の取放素子122を有する。

(もっと読む)

半導体装置

【課題】基板コストが低減でき、基板側辺の露出による剥離を改善可能な半導体装置を提供する。

【解決手段】小基板を有する多チップメモリの実装構造を有する半導体装置100の基板120は、チップ搭載体110の下方に貼り付けられ、上表面121および下表面122を有する。上表面121は、中空エリア11に露出する。下表面122には、複数の接触パッド123が設置される。第1チップ130は、基板120上に設置されて中空エリア111の内に位置する。第2チップ140は、チップ搭載体110上に設置される。封止体150は、チップ搭載体110、基板120の上表面121、第1チップ130、および、第2チップ140を密封する。基板120の外形は、封止体150の外形よりも小さく、チップ搭載体110の周辺では複数の支持バー112と接続する。支持バー112群は、封止体150の側辺へ延びる。

(もっと読む)

半導体パッケージ及びその実装方法

【課題】より優れる側面電磁遮蔽効果を有する半導体パッケージ及びその実装方法を提供する。

【解決手段】半導体実装方法により、基板ユニット213を有するマザー基板を提供し、基板ユニット213の角隅に接地連結の位置合わせマーク215を設置する。基板ユニット213の上にチップ220を設置する。マザー基板の上表面211に封止体230を形成して基板ユニット213と分割ラインとを連続被覆する。マザー基板の下表面212に分割ラインに沿って少なくともマザー基板を貫通する複数の半切断溝240を形成する。位置合わせマーク215を被覆連結するようにマザー基板の下表面212と半切断溝群240とに第一電磁遮蔽層251をパターン化形成する。封止体230を個片化分割した後、封止体230の頂面231と分割側面232とに第一電磁遮蔽層251と連結する第二電磁遮蔽層252を形成する。

(もっと読む)

非アレイバンプのフリップチップモールドの構造体及び方法

【課題】モールド工程において、モールド流れの導きと流速バランス取りが可能な非アレイバンプのフリップチップモールドの構造体を提供する。

【解決手段】基板110は、はんだマスク層112に覆われる上表面111を有し、複数のパッド113と少なくとも1つのモールド流れガイドバー114を設置する。モールド流れガイドバー114は、パッド無し空白区域Aに設置され、かつパッド113とはんだマスク層112を越える高さHを有して突起状に形成される。チップ120は複数個のバンプ121を有し、かつ基板110上にフリップチップ接合されることで、バンプ群121をパッド群113に接合させ、チップ120と基板110との間にモールド流れ間隙Sを形成する。モールド封止材130は上表面111に形成されてチップ120を密封し、モールド流れ間隙Sに十分充填されてバンプ群121とモールド流れガイドバー114を密封している。

(もっと読む)

半導体製造設備における異常予測制御装置及び方法

【課題】半導体製造設備の寿命追跡および損傷予測を行い、設備ダウンと修復の時間を削減し、製品の大量異常を予防することができる半導体製造設備における異常予測制御装置および方法を提供する。

【解決手段】半導体製造設備100における異常予測制御装置200は、第一振動検出器220と振動スペクトル解析装置240との間に接合される多重チャンネル伝送器210とを有する。多重チャンネル伝送器210は、複数の信号接続端子213を有する多重チャンネル接合モジュール212を含む。信号接続端子213は、第一振動検出器220および第一制御信号接続ワイヤ230と接続され、第一回転型周波数変換装置110に対応する第一コントローラ120に接続される。これにより、半導体製造設備の寿命追跡及び早め損傷予知を執行することができ、設備ダウンと修復の時間を減少することができる。

(もっと読む)

落下試験装置及びその使用方法

【課題】半導体チップパッケージ製品の落下試験装置及びその使用方法を提供する。

【解決手段】落下試験装置100は、水平移動ができるように固定ラック110に設置され、被試験デバイス(device under test、DUT)10を所定の角度に照準することが可能となり、且つクランプ130に正確、快速及び安全に固定されることを特徴とする落下開始角度設定治具120を有する。このような治具は、第二基準面123を提供して昇降調節可能の試験サンプル台121に連結する。試験サンプル台121は第一基準面122を有することにより、DUT10はクランプ130に挟まれた後に、摩擦が起きなく移動もしないように治具120から着脱することができる。従って、DUT10は精確に位置決められるだけではなく、治具120は滑りレールとストッパとの設計を用い迅速及び安全に参考位置に戻ることができる。

(もっと読む)

ウインドウ型半導体パッケージ

【課題】一種のモールド流入口に剥離現象の発生を避けるウインドウ型半導体パッケージを提供する。

【解決手段】半導体パッケージは、主に1つの基板、基板に貼り付ける一主面を有する1つのチップ、チップと基板の基板コア層とを接着する1つのダイアタッチング層、複数のボンディングワイヤ及び1つのモールド封止体を含む。基板のスロットの一端にチップ寸法を超える1つのモールド流入口を形成し、二個、または、これより多いモールド流れ障害物は、基板コア層上に付着してダイアタッチング区域の一縁部とスロットの両側縁との交差部位に位置し、更に、モールド流入口の両側に僅かに突出するためモールド流れによる衝撃はダイアタッチング層に加える応力を抵抗してモールド流入口に剥離現象の発生を避けると共に、ダイアタッチング間隙を維持することも可能である。

(もっと読む)

ウインドウ型BGAパッケージ及びその製造方法

【課題】側面の剥離や断裂等を抑制するウインドウ型BGAパッケージを提供する。

【解決手段】基板210、第一チップ220、ダイアタッチ部材230、複数の第一ボンディングワイヤ240、封止体250及び複数の外接端子260を備える。基板210はダイアタッチ凹部213及びスロット214を有する。第一チップ220は、ダイアタッチ凹部213に設置され、側面223を有する。ダイアタッチ部材230はダイアタッチ凹部213の内に形成される。ダイアタッチ凹部213はダイアタッチ部材230の形状を制限し、ダイアタッチ部材230が側面223群と周縁213Aとの間の間隙に充填され、且つ側面223群の一部を被覆する。第一ボンディングワイヤ240群はスロット214を通過して第一チップ220と基板210とを電気接続する。封止体250は第一チップ220と第一ボンディングワイヤ240群とを密封する。

(もっと読む)

半導体パッケージの基板およびそれを用いた半導体パッケージ

【課題】ダイアタッチング剤の気泡の残留およびオーバーフローを防止可能な半導体パッケージの基板を提供する。

【解決手段】基板本体310の表面311上に、第一組フィンガー321群、第二組フィンガー322群および第三組フィンガー323群を設ける。第一組フィンガー321群は第二組、第三組フィンガー322、323郡との間に位置する。はんだマスク層330は表面311に形成され、第一組、第二組、第三組フィンガー321、322、323群をそれぞれ露出する第一開口331、第二開口332および第三開口333を有する。第一排気溝部340は、はんだマスク層330の露出表面に形成され、はんだマスク層330を貫通せず、第一開口331に接続して表面311の側辺313、314に伸び、第二開口332と第三開口333とに連結しない。このように、ガスを外部へ排出する通路を有するため、ダイアタッチング剤の気泡の残留を防止できる。

(もっと読む)

1 - 10 / 36

[ Back to top ]