エス テ マイクロエレクトロニクス エス アーにより出願された特許

1 - 10 / 11

アナログ/デジタル変換器

【課題】アナログ/デジタル変換器のビット数を、複雑さ又は処理時間を過度に増加させずに増加させることを目的とする。

【解決手段】アナログ信号をn ビットのデジタルデータに変換するアナログ/デジタル変換方法において、前記アナログ信号の振幅を、フルスケールアナログ信号の振幅を2k(k; nより小さい整数)で除算した閾値と比較する比較ステップと、前記アナログ信号をn-k ビットにアナログ/デジタル変換を行い、前記比較ステップの結果が前記アナログ信号の振幅が前記閾値より大きいことを示す場合、n ビットのデジタルデータのMSB 側のn-k ビットを得て、前記比較ステップの結果が前記アナログ信号の振幅が前記閾値以下であることを示す場合、前記n ビットのデジタルデータのLSB 側のn-k ビットを得るステップとを備える。

(もっと読む)

共振器及び共振器を形成するための方法

【課題】温度が上昇する際における共振器の周波数の著しい低下を克服する共振器及び共振器を形成するための方法を提供する。

【解決手段】共振器は、バルク21と柱状部24とを含む共振素子20を備えたバルクモード共振器である。柱状部24は、バルクの材料の温度係数の符号と反対の符号の温度係数を有するヤング率の材料から形成されている。また、柱状部24は、バルク波の振動方向に対して垂直方向に長く、共振素子20の膨張/圧縮方向に共振素子20と交差してバルク21の連続部分を有する様に分散されている。

(もっと読む)

可変利得RF増幅器

【課題】本発明は、RF信号が通過する構成要素の数が極めて少なく、装置の電流消費及び面積を低減することが可能な可変利得増幅器を提供する。

【解決手段】可変利得増幅器は、入力ノードと、入力ノードに接続されている可変電流源と、第1供給端子及び可変電流源間に並列に接続されており、第1差動利得信号及び第2差動利得信号によって制御されるべく配置されている差動対を構成し、その一方が可変利得増幅器の出力ノードを有している第1出力端子及び第2出力端子を含む第1分岐回路及び第2分岐回路と、第1出力端子及び第2出力端子に接続されており、更にコンデンサを介して入力ノードにも接続されている中間ノードを含む分圧器とを備える。

(もっと読む)

時間測定のための電荷保持要素を読み取る回路

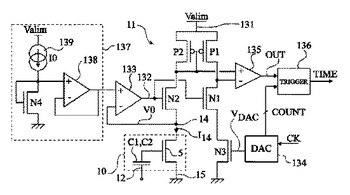

【解決手段】本発明は、その誘電体がリークを示す少なくとも1つの容量性素子(C1,C2) と、残留電荷を読み取るための絶縁された制御ターミナル(5) を含むトランジスタとを備えたタイプの時間測定のための電荷保持電子要素(10)を読み取るための方法及び回路に関し、前記読み取り回路は、第1タイプの少なくとも1つのトランジスタ(P1,P2) と、第2タイプの1つのトランジスタ(N3,5)とを夫々含む、2つの供給ターミナル間の2つの平行な分岐を備えており、前記分岐の一方の第2タイプのトランジスタは、読み取られるべき前記要素のトランジスタから構成されており、前記分岐の他方の第2タイプのトランジスタは、該トランジスタの制御ターミナルでステップ信号(VDAC)を受けており、第1タイプのトランジスタの夫々のドレインは、比較器(135) の夫々の入力に接続されており、比較器の出力(OUT) が、電荷保持要素における残留電圧の表示を与える。  (もっと読む)

(もっと読む)

時間測定のための電荷保持回路のプログラミング

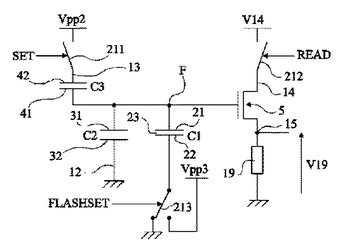

【解決手段】本発明は、その誘電体がリークを有する少なくとも1つの第1容量性素子(C1)と、その誘電体が第1容量性素子のキャパシタンスより大きいキャパシタンスを有する少なくとも1つの第2容量性素子(C2)とを備えた時間測定のための電荷保持電子回路であり、前記2つの素子は、残留電荷を測定するために、素子(5) に接続可能なフローティングノード(F) を構成する共通電極を有する前記電荷保持電子回路を制御する方法に関し、電荷保持期間が、第1容量性素子を介した充電又は放電によりプログラミング又は初期化される。  (もっと読む)

(もっと読む)

時間測定のための電荷保持回路

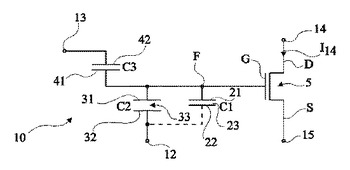

【解決手段】本発明は、時間測定のための電荷保持回路に関し、電荷保持回路は、その第1電極(21)がフローティングノード(F) に接続された少なくとも1つの第1容量性素子(C1)と、その第1電極(31)が前記フローティングノード(F) に接続された少なくとも1つの第2容量性素子(C2)と、前記フローティングノードに接続され、絶縁された制御ターミナルを有する少なくとも1つの第1トランジスタ(5) とを備え、第1容量性素子は誘電体スペーサ(23)を通したリークを有し、第2容量性素子は第1容量性素子のキャパシタンスより大きいキャパシタンスを有する。  (もっと読む)

(もっと読む)

時間測定のためのEEPROM電荷保持回路

【解決手段】本発明は、選択トランジスタをフローティングゲート・トランジスタと直列に夫々備えるEEPROMメモリセルのアレイに埋め込まれている時間測定のための電荷保持電子回路に関し、前記回路は、メモリセルのいずれか1つの列に、そのフローティングゲート・トランジスタのトンネル窓の誘電体の厚さが、他のセルのフローティングゲート・トランジスタのトンネル窓の誘電体の厚さより薄い少なくとも1つの第1セル(C1)から成る第1サブアセンブリと、そのフローティングゲート・トランジスタのドレイン及びソースが相互接続されている少なくとも1つの第2セル(C2)から成る第2サブアセンブリと、少なくとも1つの第3セル(7) から成る第3サブアセンブリと、そのトンネル窓が除去された少なくとも1つの第4セル(6) から成る第4サブアセンブリとを備え、前記4つのサブアセンブリのセルのトランジスタのフローティングゲートが夫々相互接続されている。  (もっと読む)

(もっと読む)

基板から離間した単結晶半導体膜部分の形成

【課題】空隙領域の上にファセットのない単結晶半導体膜を形成し、デバイス表面積の減少を防ぐ薄い単結晶膜の積層構造、及び、チャネル領域が均一な厚みを有し、均一な厚みの少なくとも一層の非単結晶膜で下部の半導体ウエハから離間しているMOSトランジスタの製造方法を提供する。

【解決手段】絶縁領域34内部に、選択的なエピタキシャル成長により単結晶半導体活性領域上に単結晶半導体犠牲膜38及び前記単結晶半導体膜40を成長させ、隆起した前記絶縁領域34を少なくとも部分的に除去し、側面から前記単結晶半導体犠牲膜38の除去を実施する。その後空隙を残す形態。絶縁体、電気伝導体、または熱伝導体で充填する。

(もっと読む)

酸化シリコン層の選択的除去

【解決手段】本発明は、装置を製造する方法に関し、前記装置の第1領域内に第1酸化シリコン層を形成し、前記装置の第2領域内に第2酸化シリコン層を形成するステップと、前記第1領域内に第1タイプのドーピングイオンを注入するステップと、前記第2領域内に第2タイプのドーピングイオンを注入するステップと、前記第1酸化シリコン層が除去され、前記第2酸化シリコン層の少なくとも一部が残るように、定められた継続時間前記第1及び第2領域をエッチングするステップとを備える。  (もっと読む)

(もっと読む)

燃料電池及びウエハ

【課題】 本発明の目的は、乾燥しない電解質を備えた燃料電池を提供することにある。

【解決手段】 本発明は、電解質層6の両側にそれぞれ積層された第1及び第2触媒層5、7にはそれぞれアノード10及びカソード12が接続され、第1触媒層5には水素が供給され、第2触媒層7には酸素が供給され、親水性層20は第2触媒層7を被覆するように設けられ、酸素は前記親水性層20を通して第2触媒層7に供給されている燃料電池を提供する。

(もっと読む)

1 - 10 / 11

[ Back to top ]