テキサス インスツルメンツ インコーポレイテッドにより出願された特許

41 - 50 / 50

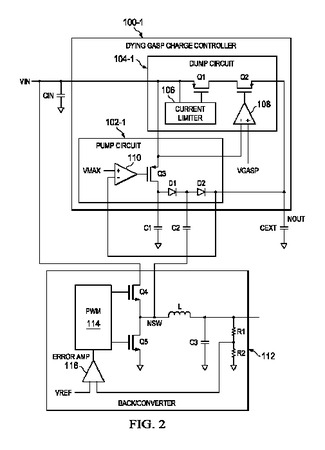

電力シャットダウン充電コントローラ

滞りなくシャットダウンを可能にするのに充分長い時間の間シャットダウン時にエネルギーを供給するため、入力ノード(NIN)、入力ノードに結合される内部コンデンサ(CINT)、出力ノード(NOUT)、「dying gasp」電力シャットダウン充電コントローラ(100)を含む装置が開示される。充電コントローラ(100)は、ダンプ回路(104)及びポンプ回路(102)を含む。ダンプ回路(104)は、出力ノード(NOUT)の電圧がプリチャージ電圧より低いとき、スタートアップ時に入力ノード(NIN)から出力ノード(NOUT)にチャージを供給する。ダンプ回路(104)は、入力ノードの電圧がgasp電圧(VGASP)を下回るとき、出力ノードから入力ノードにチャージを供給する。ポンプ回路(102)は、出力ノード(NOUT)の電圧が充電電圧(VMAX)より低いとき、入力ノード(NIN)から出力ノード(NOUT)にチャージを供給する。

(もっと読む)

(もっと読む)

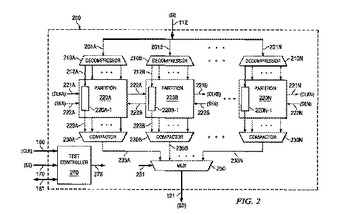

パーティションを設けたスキャン・チェーンを備えた集積回路のスキャンテストにおける向上した制御

パーティションを設けたスキャン・チェーンを備えた集積回路(IC)に実装されたテスト・コントローラが、スキャンテストを実行する際に向上した制御を提供する。一つの側面に従って、テスト・コントローラは、独立しているべき、ICの異なるスキャン・チェーンに対するスキャンテストのスキャンイン、スキャンアウト、及びキャプチャ位相を選択的に制御できる。外部テスターとインタフェースするためにテスト・コントローラに必要なピンの数は、そのテスト・コントローラがサポートし得るパーティションの数より少ない。別の側面に従って、ICは、遷移故障(又はLOS)テストをサポートするため各パーティションに対応するレジスタを含む。別の側面に従って、パーティションを設けたスキャン・チェーンを備えたICが、シリアル−パラレル及びパラレル−シリアル変換器を含み、それにより、スキャンテストをサポートするために必要とされる外部ピンを最小限にする。  (もっと読む)

(もっと読む)

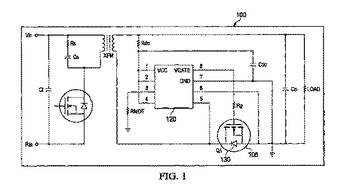

同期整流器制御のシステム及び方法

同期整流器制御のためのシステム及び方法が提供される。同期整流器は、寄生ドレイン・インダクタンス及び寄生ソース・インダクタンスを含む。寄生インダクタンスの影響を相殺するため、補償インダクタンスが導入される。補償インダクタンスは、半導体ダイ上のトレース・インダクタンスから形成され得る。或る半導体パッケージにおいて、寄生インダクタンスは実質的に固定されて、そのレイアウトが、固定された補償インダクタンスを生成するように変更され得るようにしてもよい。  (もっと読む)

(もっと読む)

ショート及びロング・トレーニング・フィールド

同期化ヘッダーの一部としてショート・トレーニング・フィールドを及び前記同期化ヘッダーの一部としてロング・トレーニング・フィールドを含むパケットを生成(710)し、更に、無線ネットワーク内の通信のため前記パケットを用いる(712)ように構成されるロジックを含む、集積回路。  (もっと読む)

(もっと読む)

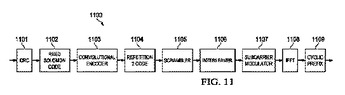

連接反復符号を用いる畳み込み符号

信号を変調し符号化するシステムおよび方法が開示される。メディアアクセス制御(MAC)層からのデータが畳み込み符号化される(1103)。MAC層からのデータのロバストな符号化(1102、1104)が、この畳み込み符号化(1103)の前または後に実施される。符号化されたデータは差動変調され(1107)、次いで、直交周波数分割多重化されて(1108)、電力線ネットワーク上を送信されるのに適合したOFDM出力信号が生成される。ロバストな符号化は、反復2符号化(1104)または反復N符号化(1104)とし得る。ロバストな符号化は、畳み込み符号化(1103)の前に外部符号(1102)を付加してもよい。ロバストな符号化は、畳み込み符号化(1103)の前に実施されるリードソロモン符号化(1102)としてもよい。ロバストな符号化を識別するためのオプションのヘッダ(702)も、ヘッダ(702)を復号する方法とともに開示する。  (もっと読む)

(もっと読む)

3相モードのOFDM伝送方法

トランスミッタ(301)及びレシーバ(302)が電力線(303)の一つ又はそれ以上の位相(31、32、33)に接続される電力線伝送のためのシステム及び方法が開示される。前記電力線ネットワーク(303)で送信されるべき少なくとも1つのシンボル・ストリーム(x)が生成される。前記少なくとも1つのシンボル・ストリーム(x)は、重みベクトルを用いてスケーリングされて、複数のスケーリングされたシンボル・ストリーム(s1、s2、s3)を生成する。前記重みベクトルは、それぞれ前記電力線ネットワーク(303)の位相(31、32、33)に対応する、複数の重み(υ1、υ2、υ3)を含む。前記スケーリングされたシンボル・ストリーム(s1、s2、s3)の各々は、前記電力線ネットワーク(303)の対応する位相(31、32、33)で送信される。ゼロクロス検出器(1411)が、レシーバ(1312a〜n)のための位相情報を識別する。コンセントレータ(1314)は、前記レシーバ(1312a〜n)に関連する前記位相に基づいて前記レシーバ(1312a〜n)へ送信されるよう信号を適合させる。  (もっと読む)

(もっと読む)

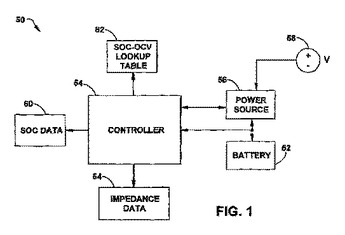

バッテリー充電状態を判定するためのシステム及び方法

バッテリー(52、102、150、202)の充電状態を判定するためのシステム(50、200)及び方法が提供される。前記システム(50、200)は、バッテリー(52、102、150、202)に充電電流を供給するように構成される電源(56、206)を含む。コントローラ(54、104、204)が含まれ、インピーダンスに基づく期間の間のバッテリー(52、102、150、202)のインピーダンスに基づいたバッテリー(52、102、150、202)の充電状態、及び充電期間の間のバッテリー(52、102、150、202)の充電状態関係を判定するように構成される。

(もっと読む)

(もっと読む)

マスクなし多重シートポリシリコン抵抗器

【課題】 半導体デバイス、特に、ポリシリコン抵抗器及びその製作に関する技術を提供する。

【解決手段】 本発明は、余分な半導体製作工程段階を追加する必要なしに、異なるシート抵抗値のポリシリコン抵抗器を有する半導体デバイスの製作を可能にする。半導体デバイスの上に酸化物層が形成される(104)。酸化物層上にポリシリコン層が形成される(106)。ポリシリコン層は、ポリシリコン抵抗器を形成するためにパターン化される(108)。ポリシリコン抵抗器の選択した割合が露出したポリシリコン抵抗器マスクが、ポリシリコン抵抗器上に形成される(110)。選択されたドーパントが注入され(112)、これが、ポリシリコン抵抗器の抵抗率を修正する。マスクが除去され(114)、ポリシリコン抵抗器を通して実質的に均一な濃度まで注入ドーパントを拡散する熱活性化処理が行われる(116)。

(もっと読む)

反射防止誘電体を有する集積回路コンデンサ

【課題】半導体素子及び特にコンデンサの誘電体が反射防止材料を含む集積回路コンデンサを提供する。

【解決手段】集積回路(IC)製造工程の一部として形成されるコンデンサ(100)。コンデンサは、導電上部及び下部電極(140、144)と非導電コンデンサ誘電体(142)とを有する。一例において、誘電体は、反射防止材料(118)の層を挟む第1及び第2の薄い誘電体層(112、114)を含む。これらの薄い層は、コンデンサに必要な誘電挙動をもたらし、一方、反射防止層は、とりわけ、反射された定常波を軽減することによって形態サイズの縮小を容易にする。

(もっと読む)

基板傾斜を用いた半導体ドーピング

【課題】半導体基板をドープする方法、特に、注入源に対する基板の傾斜角を変えることによってドーパントを注入する方法を提供する。

【解決手段】基板にドーパントを注入する方法、及びそのような注入を利用して半導体素子を製造する方法。ドーパントを注入する方法は、他の段階の中でもとりわけ、注入プラテン(305)上又はその上に位置する基板(310)を注入源(320)に対して第1の方向の軸線に関して傾斜させる段階と、第1の方向に傾斜した基板(310)を使用して注入線量の一部分を注入する段階と、次に、基板(310)を第1の方向と反対の第2の方向に傾斜させる段階と、第2の方向に傾斜した基板(310)を使用して注入線量の別の部分を注入する段階とを含む。

(もっと読む)

41 - 50 / 50

[ Back to top ]