ドンブ ハイテック カンパニー リミテッドにより出願された特許

1 - 10 / 189

イメージセンサ及びその製造方法

【課題】イメージセンサ及びその製造方法を提供すること。

【解決手段】イメージセンサは、リードアウト回路120を含む半導体基板100と、前記リードアウト回路120に接続されるように、前記半導体基板100上に形成された配線150及び層間絶縁層160と、前記層間絶縁層160上に形成されたイメージ感知部と、前記配線150に対応するように、前記イメージ感知部に形成されたトレンチと、前記トレンチの側壁に形成されたバッファ層と、前記バッファ層上に形成され、前記トレンチの底面を選択的に露出させるバリアパターンと、前記配線が露出するように、前記バリアパターンの下部の前記イメージ感知部及び層間絶縁層を貫通するビア孔と、前記ビア孔の内部に形成されたメタルコンタクトとを備える。

(もっと読む)

半導体素子の製造方法

【課題】静電気防止素子のノーマルコンタクトと半導体素子のブランケットコンタクトを同時に形成する。

【解決手段】本発明の半導体素子の製造方法は、基板上に静電気防止素子に対するアクティブ領域と、第1ポリゲート及び半導体素子に対するアクティブ領域と、ブランケットトレンチ形態の第2ポリゲートとを形成する段階と、前記基板上に第1絶縁膜と第2絶縁膜を含む層間絶縁層を形成する段階と、前記層間絶縁層に平坦化工程を行う段階と、前記第1ポリゲート上に形成された層間絶縁層の一部を開口させたコンタクトパターンを形成する段階と、前記コンタクトパターンの下の第2絶縁膜を第1エッチングして第1ポリゲート上のトレンチを形成する段階と、第2エッチングを行って前記第1ポリゲート上のトレンチ内部の第1絶縁膜を除去し、前記第2ポリゲートを除いた前記半導体素子のアクティブ領域上の第1絶縁膜を除去する段階とを含む。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子及びその製造方法を提供する。

【解決手段】この半導体素子の製造方法は、半導体基板に第1導電型不純物イオンを注入して第1ウェルを形成する段階、半導体基板に第2導電型不純物を注入して、第1ウェルの一領域と重なる拡張されたドレインを形成する段階、半導体基板に第2導電型不純物を注入して、拡張されたドレイン下部の半導体基板内に、第1ウェルの他の領域と重なるようにして第1導電型の第2ウェルを形成する段階、拡張されたドレインと一部重なる第1ウェル上にゲートを形成する段階、及びゲートの一側における拡張されたドレイン領域に第2導電型不純物を注入してドレイン領域を形成する段階と、を含む。

(もっと読む)

イメージセンサ及びその製造方法

【課題】イメージセンサ及びその製造方法を提供すること。

【解決手段】イメージセンサは、単位ピクセル別にリードアウト回路120の形成された半導体基板100と、前記半導体基板100上に形成された層間絶縁層160と、前記リードアウト回路120にそれぞれ接続されるように、前記層間絶縁層160を貫通して形成された配線150と、前記配線150にそれぞれ接続されるように、前記層間絶縁層160上に形成された第1金属パターンと、前記第1金属パターン上に形成された第2金属パターンと、前記第2金属パターン上に形成されたフォトダイオードパターンとを含む。

(もっと読む)

半導体メモリセル及び半導体メモリセルの製造方法、半導体メモリセルの動作方法

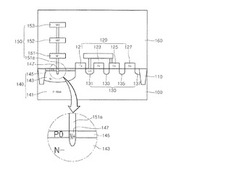

【課題】単一ポリEEPROMセルをスタックゲートポリEEPROMセルの水準にスケーリングできる半導体メモリセルを提供する。

【解決手段】単一ポリEEPROMセルは、フローティングゲートFG上にカップリングのためのコンタクトを形成させ、コンタクトはコントロールゲートCGラインによりワードライン用ポリシリコンWLの方向に連結される。このコンタクトとフローティングゲート用ポリシリコンFGとの間にカップリングのための誘電膜102を形成してフローティングゲート用ポリシリコンFGとコンタクトを通じてカップリングを実施する。また、この半導体メモリセルで、プログラム、消去、読み出しが可能なように動作させる。

(もっと読む)

不揮発性メモリ素子及びその駆動方法

【課題】プログラム及び消去動作部分と読み出し動作部分とを分離させることによって、耐久性またはサイクル特性を画期的に改善させる不揮発性メモリ素子及びその駆動方法を提供する。

【解決手段】単一ポリEEPROMの不揮発性メモリ素子は、第1タイプウェル10上に形成されるフローティングゲート50と、第2タイプウェル20上に形成されるとともにフローティングゲート50と直列連結される複数のトランジスタ30,40と、を備え、これらのトランジスタ30,40のうち、いずれかひとつはプログラム及び消去のための第1トランジスタ30であり、他のひとつは読み出し(reading)のための第2トランジスタ40である。

(もっと読む)

半導体素子の製造方法

【課題】タングステン等のCMP(化学機械研磨)後、エロージョン量をモニタリングできるパターンを提示する。

【解決手段】ホールアレイサイズスプリットaと配列間スペースの長さスプリットbを一定に規定したモニタリングパターンを利用して、プラグCMP時に発生するエロージョンレベルを評価する。前記ホールアレイサイズによる影響はホールアレイサイズに応じて増加するため、エロージョン量は特定のサイズにおいて飽和になるのかをモニタリングする。また前記配列の間で影響を受けるスペースの長さをモニタリングする。

(もっと読む)

半導体素子の金属構造物再形成方法

【課題】コンタクトプラグ、及び金属配線のような金属構造物に欠陥が発生して再形成工程を処理する場合、コンタクトホールが過度に露出されてホールが大きくなる現象を防止できる金属構造物の再形成方法を提供する。

【解決手段】本発明に従う金属構造物の再形成方法は、コンタクトプラグを含む絶縁層の上に形成された第1金属層、第1金属層の上に形成された金属配線層、金属配線層上に形成された第2金属層を含む金属構造物の再形成方法に関するものであって、第1ウェットエッチング工程を処理して金属配線層の下を除外した第1金属層及び第2金属層を除去するステップと、第2ウェットエッチング工程を処理して金属配線層を除去するステップと、第1平坦化工程を処理して残存した第1金属層及び絶縁層の表面を平坦化するステップと、を含む。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子及びその製造方法を提供する。

【解決手段】この半導体素子の製造方法は、半導体基板に第1導電型不純物を注入する第1インプラント工程を行い、第1導電型の第1ウェルを形成する段階と、第2導電型不純物を第1導電型の第1ウェルに注入する第2インプラント工程を行い、第1導電型の第2ウェルを形成する段階と、第2導電型不純物を第1導電型の第2ウェルに注入する第3インプラント工程を行い、第2導電型不純物領域を形成する段階と、半導体基板上にゲートを形成する段階と、第2導電型不純物を注入する第4インプラント工程を行い、ゲートの一側の第2導電型不純物領域内にドレイン領域を形成する段階と、を含む。

(もっと読む)

フラッシュメモリ素子の製造方法

【課題】フラッシュメモリ素子の製造方法を提供する。

【解決手段】セル領域及び周辺領域を含む半導体基板10を用意するステップと、半導体基板10のセル領域に第1ウェルを形成した上でONO膜を形成するステップと、第1ウェルを含む半導体基板10の周辺領域に第2ウェルを形成した上で第1酸化膜21を形成するステップと、第1ポリシリコン膜51を形成した後にONO膜パターン及び第1ポリシリコンパターン61から形成されたメモリゲートを形成するステップと、メモリゲートの両側壁に第2酸化膜パターン26及び第2ポリシリコンパターン62(残留パターン)を形成した上でゲートを形成するステップと、メモリゲートの片方側壁のみに残留パターンを残してセレクトゲートを形成するステップと、互いに隣接したメモリゲートの間の半導体基板10に第3不純物領域15を形成するステップとを含む。

(もっと読む)

1 - 10 / 189

[ Back to top ]