スタッツ チップパック リミテッドにより出願された特許

1 - 6 / 6

フリップチップ半導体ダイのパッドレイアウトを形成する半導体素子および方法

【課題】半導体素子を作製する方法を提供する。

【解決手段】主に半導体ダイの周辺領域中に位置する信号パッドと、主に前記信号パッドから半導体ダイの内部領域中に位置する電力パッドおよび接地パッドとを伴う、ダイパッドレイアウトを有する半導体ダイを提供するステップと、前記信号パッド、電力パッド、および接地パッド上に複数のバンプを形成するステップと、基板を提供するステップと、前記基板上に相互接続部位を伴う複数の伝導性トレースを形成するステップであって、前記バンプは、相互接続部位よりも幅広い、ステップと、前記バンプが前記相互接続部位の頂面および側面を覆うように、前記バンプを前記相互接続部位に接着するステップと、前記半導体ダイと基板との間で前記バンプの周囲に封入材を堆積させるステップとを含む、半導体素子を作製する方法。

(もっと読む)

バンプオンリード相互接続を形成する半導体素子および方法

【課題】半導体素子を作製する方法を提供する。

【解決手段】半導体ダイの表面上に形成された複数の複合バンプを有する、半導体ダイを提供するステップであって、前記複合バンプは、可融性部分および非可融性部分を有する、ステップと、基板を提供するステップと、エスケープルーティング密度を増加させるための平面図から、伝導性トレースと平行な縁を有する相互接続部位を伴って前記基板上に複数の伝導性トレースを形成するステップであって、前記複合バンプは、前記相互接続部位よりも幅広い、ステップと、前記可融性部分が前記相互接続部位の頂面および側面を覆うように、前記複合バンプの前記可融性部分を前記相互接続部位に接着するステップと、前記半導体ダイと基板との間で前記複合バンプの周囲に封入材を堆積させるステップとを含む、半導体素子を作製する方法。

(もっと読む)

半導体素子およびフリップチップ相互接続構造を形成する方法

【課題】半導体素子を作製する方法を提供する。

【解決手段】半導体ダイの能動表面上に形成された複数のバンプを有する、半導体ダイを提供するステップと、基板を提供するステップと、前記基板上に相互接続部位を伴う複数の伝導性トレースを形成するステップであって、前記バンプは、前記相互接続部位よりも幅広い、ステップと、前記接続部位から離れた前記基板の領域上にマスキング層を形成するステップと、前記バンプが前記相互接続部位の頂面および側面を覆うように、前記バンプを前記相互接続部位に接着するステップと、前記半導体ダイと基板との間で前記バンプの周囲に封入材を堆積させるステップと、を含む、半導体素子を作製する方法。

(もっと読む)

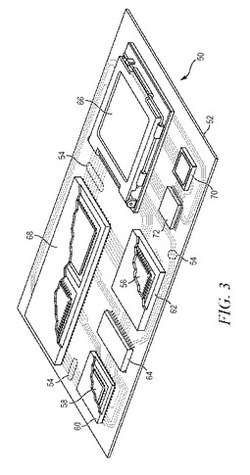

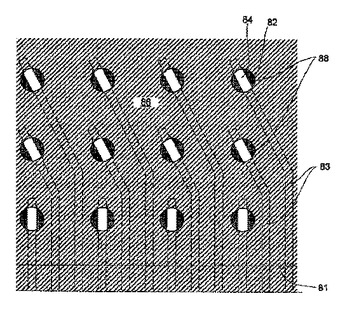

基板上に狭い配線部分を有するフリップチップ配線

【課題】フリップチップ配線を提供すること。

【解決手段】基板上のダイのフリップチップ配線は、配線の隆起を、キャプチャパッド上にではなく、リードまたはトレースの上の狭い配線パッドの上に嵌合することによってなされる。狭い配線パッドの幅は、取り付けられるダイ上の隆起のベース直径未満である。また、フリップチップパッケージは、活性表面において配線パッドに取り付けられた半田の隆起を有しているダイと、ダイ取り付け表面において導電性トレースの上に狭い配線パッドを有している基板とを含んでおり、上記基板における隆起は、トレース上の狭いパッドに嵌合される。

(もっと読む)

部分パット上にバンプを有するフリップチップ相互接続構造を形成する半導体デバイスおよびその方法

【課題】半導体素子を作製する方法を提供する。

【解決手段】半導体ダイの表面上に形成された複数のバンプを有する、半導体ダイを提供するステップと、基板を提供するステップと、露出側壁を有し、SRO+2*SRR−2Xによって定義される設計規則に従ってサイズ決定される相互接続部位を伴って、前記基板上に複数の伝導性トレースを形成するステップであって、式中、SROは、前記相互接続部位上の開口部であり、SRRは、製造工程のための位置合わせであり、Xは、接触パッドの前記露出側壁の厚さの関数である、ステップと、前記バンプが前記相互接続部位の頂面および側面を覆うように、前記バンプを前記相互接続部位に接着するステップと、前記半導体ダイと基板との間で前記バンプの周囲に封入材を堆積させるステップとを含む、半導体素子を作製する方法。

(もっと読む)

基板上に狭い配線部分を有するフリップチップ配線

基板上のダイのフリップチップ配線は、配線の隆起を、キャプチャパッド上にではなく、リードまたはトレースの上の狭い配線パッドの上に嵌合することによってなされる。狭い配線パッドの幅は、取り付けられるダイ上の隆起のベース直径未満である。また、フリップチップパッケージは、活性表面において配線パッドに取り付けられた半田の隆起を有しているダイと、ダイ取り付け表面において導電性トレースの上に狭い配線パッドを有している基板とを含んでおり、上記基板における隆起は、トレース上の狭いパッドに嵌合される。  (もっと読む)

(もっと読む)

1 - 6 / 6

[ Back to top ]