サンディスク スリーディー,エルエルシーにより出願された特許

1 - 10 / 86

側壁構造化スイッチャブル抵抗器セル

【課題】抵抗を大きくして感知されやすくするとともに、リセット電流を小さくし、製造中の損傷も抑制できる抵抗率スイッチング素子を提供する。

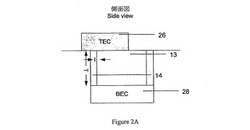

【解決手段】第1の伝導性電極28を形成するステップと、第1の伝導性電極28の上に絶縁構造13を形成するステップと、絶縁構造の側壁上に抵抗率スイッチング素子14を形成するステップと、抵抗率スイッチング素子14の上に第2の伝導性電極26を形成するステップと、第1の伝導性電極28および第2の伝導性電極26の間に抵抗率スイッチング素子14と直列にステアリング素子を形成するステップと、を含み、第1の伝導性電極28から第2の伝導性電極26への第1の方向における抵抗率スイッチング素子14の高さTは第1の方向に垂直な第2の方向における抵抗率スイッチング素子14の厚さIより大きい。

(もっと読む)

断面積が減じられたカーボンスイッチング材料を有するメモリセルとそのメモリセルを形成する方法

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

金属酸化物抵抗率スイッチング層と共に使用する下部電極

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

金属酸化物抵抗率スイッチング層と共に使用する下部電極

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

可逆的抵抗性スイッチング素子のためのステップ・ソフト・プログラム

メモリセルを形成、リセット、またはセットするための方法およびシステムが開示される。可逆的抵抗性スイッチング素子を有するメモリセルに適用される1つ以上のプログラミング条件が、メモリセルの抵抗に基づいて決定される。1つ以上のプログラミング条件の決定は、メモリセルの性質に基づく所定アルゴリズムに基づいてもよい。1つ以上のプログラミング条件は、プログラミング電圧および電流の制限を含んでもよい。例えば、プログラミング電圧の大きさは、抵抗に基づいてもよい。別例として、プログラミング電圧パルスの幅は、抵抗に基づいてもよい。一部の実施形態では、プログラミング時に使用される電流の制限が、メモリセルの抵抗に基づいて決定される。 (もっと読む)

炭素/トンネル障壁/炭素・ダイオード

炭素/トンネル障壁/炭素・ダイオード及び炭素/トンネル障壁/炭素・ダイオードの形成方法を開示する。炭素/トンネル障壁/炭素はメモリアレイ内でステアリング素子として用いられてもよい。メモリアレイ内の各メモリセルは可逆的抵抗性スイッチング素子、及びステアリング素子として炭素/トンネル障壁/炭素・ダイオードを含んでいてもよい。トンネル障壁は半導体又は絶縁体を含んでいてもよい。従って、ダイオードは炭素/半導体/炭素・ダイオードであってもよい。ダイオード内の半導体は真性であってもよいし、ドープされていてもよい。ダイオードが平衡状態にある場合は、半導体が空乏化されることがある。例えば、空乏領域が半導体領域の一端から他端まで延びるように、半導体が低濃度にドープされてもよい。ダイオードは炭素/絶縁体/炭素・ダイオードであってもよい。 (もっと読む)

マルチレベル・ライトワンス・メモリ・セルを備える書き換え可能メモリデバイス

本明細書に記載する実施形態は、マルチレベル・ライトワンス・メモリ・セルを備えるメモリデバイスに関する。一実施形態では、メモリデバイスは複数のマルチレベル・ライトワンス・メモリ・セルを備えるメモリアレイを有し、各メモリセルは複数の抵抗率レベルの1つにプログラム可能である。また、メモリデバイスは、メモリアレイからメモリセルのグループを選択し、メモリセルのグループに関連する1組のフラグビットを読み出すように構成された回路を含む。1組のフラグビットはメモリセルのグループが書き込まれた回数を示す。また、回路は、メモリセルのグループが書き込まれた回数に対する適切な閾値読出しレベルを選択し、グループ内の各メモリセルに対して、選択された閾値読出しレベルに基づいて、プログラムされていない単一ビット・メモリ・セルまたはプログラムされた単一ビット・メモリ・セルとしてメモリセルを読み出すように構成される。 (もっと読む)

メモリアレイの下方に配置されたセンスアンプ回路とセンス・アンプ・インターフェイス等ではないページレジスタとを有する3Dメモリ装置

不揮発性記憶デバイスは、基板と、その基板の一部分の上方に配置された不揮発性記憶素子のモノリシック3次元メモリアレイと、その不揮発性記憶素子と通信する複数のセンスアンプと、そのセンスアンプと通信する複数の一時記憶デバイスと、その一時記憶デバイスと通信するページレジスタと、1つまたは複数の制御回路と、を含む。この1つまたは複数の制御回路は、ページレジスタ、一時記憶デバイスおよびセンスアンプと通信する。センスアンプは、モノリシック3次元メモリアレイの下方にある基板上に配置される。一時記憶デバイスは、モノリシック3次元メモリアレイの下方にある基板上に配置される。ページレジスタは、モノリシック3次元メモリアレイの下方ではない領域にある基板上に配置される。センスアンプによって不揮発性記憶素子から読み出されたデータは、一時記憶デバイスに転送され、その後1つまたは複数の制御回路に応答してページレジスタに転送される。不揮発性記憶素子にプログラムされるデータは、その1つまたは複数の制御回路に応答してページレジスタから一時記憶デバイスへと転送される。 (もっと読む)

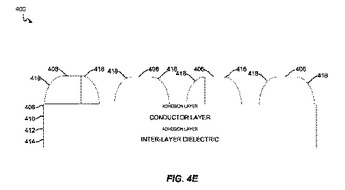

4倍ハーフピッチレリーフパターニングのための双側壁パターニングを用いたメモリ線および構造を形成する装置および方法

本発明は、4倍ハーフピッチレリーフパターニングのための双側壁パターニングを用いてメモリ線および構造を製作する装置、方法およびシステムを提供する。本発明は、基板の上方に配される第1のテンプレート層からフィーチャを形成することと、フィーチャに隣接してハーフピッチの側壁スペーサを形成することと、ハーフピッチの側壁スペーサをハードマスクとして用いることによって第2のテンプレート層内により小さいフィーチャを形成することと、より小さいフィーチャに隣接して4分の1ピッチの側壁スペーサを形成することと、4分の1ピッチの側壁スペーサをハードマスクとして用いることによって導体層から導体フィーチャを形成することとを含む。多数の追加の態様が開示される。  (もっと読む)

(もっと読む)

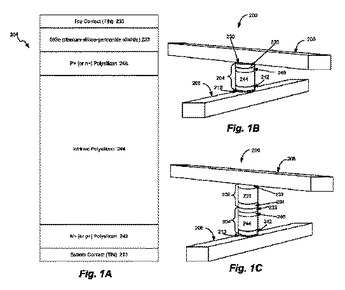

低コンタクト抵抗を有する3次元ポリシリコンダイオードおよびその形成方法

半導体p−i−nダイオードおよび半導体p−i−nダイオードを形成する方法を開示する。一形態において、一の導電型(p+またはn+の一方)を有するようにドープされた領域と、p−i−nダイオードへの電気コンタクトの間に、SiGe領域が形成される。SiGe領域は、コンタクト抵抗を低減する働きをすることができ、順バイアス電流を増加させることができる。ドープされた領域は、ドープされた領域がSiGe領域とダイオードの真性領域との間に存在するように、SiGe領域の下方を伸びている。p−i−nダイオードは、シリコンから形成することができる。SiGe領域の下方のドープされた領域は、付加されたSiGe領域によって逆バイアス電流が増加することを防止する働きをすることができる。一実施形態では、メモリアレイ内の上向きのp−i−nダイオードの順バイアス電流が、下向きのp−i−nダイオードの順バイアス電流に実質的に一致するように、SiGeは形成される。これらのダイオードが3Dメモリアレイの読み出し/書き込み材料に用いられた場合に、より良いスイッチング結果を達成することができる。  (もっと読む)

(もっと読む)

1 - 10 / 86

[ Back to top ]