ピイ・エイ・セミ・インコーポレーテッドにより出願された特許

1 - 5 / 5

統合DMA

一実施形態において、装置は、第1のインターフェース回路と、第1のインターフェース回路に結合されたダイレクト・メモリ・アクセス(DMA)コントローラと、DMAコントローラに結合されたホストとを備えている。第1のインターフェース回路はプロトコルに従ってインターフェース上で通信するように構成されている。ホストは、ホストのメモリ・システム内の複数の記憶領域に、少なくとも部分的にマッピングされた少なくとも1つのアドレス空間を備えている。DMAコントローラは、第1のインターフェース回路と、アドレス空間との間でDMA転送を実行するように構成され、DMAコントローラはさらに、複数の記憶領域のうちの第1の複数の記憶領域と、複数の記憶領域のうちの第2の複数の記憶領域との間でDMA転送を実行するように構成されている。  (もっと読む)

(もっと読む)

ギガビット/10ギガビット・イーサネット(登録商標)・システムにおける明示的フロー制御

一部の実施形態において、システムは、通信媒体と、その通信媒体に結合された第1のコントローラと、その通信媒体に結合された第2のコントローラとを含む。第1のコントローラは、パケットの第1の部分の伝送に続いて、通信媒体上で第2のコントローラへのパケットの伝送を中断するように構成される。第1のコントローラは、そのパケットの伝送を中断することに応答して、通信媒体上で少なくとも1つの制御シンボルを伝送するように構成され、第1のコントローラは、そのパケットの第2の部分から、そのパケットの伝送を続けるように構成される。コントローラは、一部の実施形態では、媒体アクセス・コントローラと、物理符号化サブレイヤとを含む。  (もっと読む)

(もっと読む)

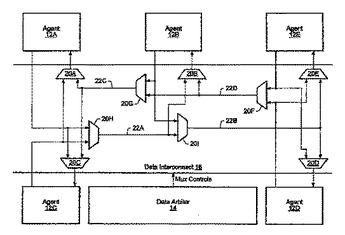

部分的にポピュレートされる階層型クロスバ

様々な実施形態で、装置は、複数のエージェントと相互接続を備える。一実施形態では、複数のエージェントは第1から第4までのエージェントを含む。相互接続は、エージェント間で通信パスを形成するように切換え可能な(例えば複数の選択回路を使用して)複数のセグメントを備え、第1セグメントは、第1エージェントから第2エージェントへの第1通信パスに含まれ、また第3エージェントから第4エージェントへの第2通信パスにも含まれる。別の実施形態では、各セグメントは選択回路によって駆動される。少なくとも1つの選択回路は、少なくとも1つのセグメントと、少なくとも1つのエージェントからの出力とを、入力として有する。さらに別の実施形態では、アービタが、セグメントを介した宛先エージェントへの通信パスを、各要求に対して相互接続上で決定するように構成される。アービタは、対応する通信パス中の各セグメントが利用可能であるような要求のサブセット間で、調停するように構成される。  (もっと読む)

(もっと読む)

浅いエージェント毎のキューを伴うブロックしないアドレス・スイッチ

一実施形態では、スイッチは、相互接続に結合されるように構成される。スイッチは、複数の記憶域及び複数の記憶域に結合されたアービタ制御回路を備える。複数の記憶域は、複数のエージェントにより送信された複数の要求を格納するように構成される。アービタ制御回路は、複数の記憶域に格納されている複数の要求の間のアービトレーションを行うように構成される。選択された要求は、アービトレーションの勝者であり、スイッチは、選択された要求を複数の記憶域のうちの1つから相互接続上に送信するように構成される。他の実施形態では、システムは、複数のエージェント、相互接続、エージェントと相互接続とに結合されたスイッチを備える。他の実施形態では、方法が考察される。  (もっと読む)

(もっと読む)

論理回路電源電圧と異なるメモリ用の別の電源電圧を有する集積回路

一実施形態では、集積回路は、第1の電源電圧が供給される少なくとも1つの論理回路と、論理回路に結合され、第2の電源電圧が供給される少なくとも1つのメモリ回路とを備える。メモリ回路は、使用時に第1の電源電圧が第2の電源電圧より小さい場合でも、論理回路に応答して読み出されかつ書き込まれるように構成される。もう1つの実施形態では、方法は、第1の電源電圧が供給される論理回路が、メモリ・セルを読み出すステップと、メモリ・セルが、第1の電源電圧を基準とする信号を用いて読み出しに応答するステップとを含み、使用時にメモリ・セルには、第1の電源電圧より大きな第2の電源電圧が供給される。  (もっと読む)

(もっと読む)

1 - 5 / 5

[ Back to top ]