モサイド・テクノロジーズ・インコーポレーテッドにより出願された特許

1 - 10 / 106

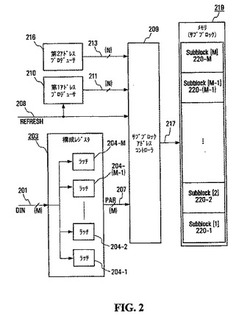

完全に独立のパーシャルアレイリフレッシュ機能を有するダイナミックランダムアクセスメモリ

【課題】独立パーシャルアレイリフレッシュ機能を有する改善されたダイナミックランダムアクセスメモリ(DRAM)を提供する。

【解決手段】DRAMデバイスが、複数のメモリサブブロックを有する。各サブブロックは、複数のワード線を有し、これらのワード線に、複数のデータ記憶セルが接続される。パーシャルアレイセルフリフレッシュ(PASR)構成セッティングが、独立に作られる。PASRセッティングに従って、メモリサブブロックが、リフレッシュのためにアドレッシングされる。PASRセッティングは、メモリコントローラによって作られる。サブブロックアドレスのすべての種類の組合せを選択することができる。したがって、メモリサブブロックは、完全に独立にリフレッシュされる。データ保持に関するユーザ選択可能メモリアレイは、特に低消費電力モバイル応用の有効なメモリ制御プログラミングをもたらす。

(もっと読む)

多数の外部電力供給部を有する不揮発性半導体メモリ

【課題】メモリ動作を可能にするために、低いまたはより低い電圧入力をより高い電圧に変換することは、変換器効率を低下させ、チャージポンプ回路のサイズおよび複雑さを増加させる。

【解決手段】メモリデバイスはデータを記憶するためのフラッシュメモリなどのコアメモリを含む。メモリデバイスは、フラッシュメモリに電力を供給するのに使用される第1の電圧を受け取るために第1の電力入力部を含む。さらに、メモリデバイスは、第2の電圧を受け取るために第2の電力入力部を含む。第2の電圧を受け取り、1つまたは複数の内部電圧を引き出すように構成された電力管理回路をメモリデバイスは含む。電力管理回路は内部電圧をフラッシュメモリに供給または伝達する。電力管理回路(例えば電圧変換器回路)によって発生され、コアメモリに供給される様々な内部電圧は、コアメモリ中のセルに関する読出し/プログラム/消去などの動作を可能にする。

(もっと読む)

揮発性メモリおよび不揮発性メモリを有するハイブリッド固体メモリシステム

【課題】データを記憶するためのハイブリッド固体メモリシステムを提供する。

【解決手段】この固体メモリシステムは、揮発性固体メモリ、不揮発性固体メモリおよびメモリ制御部を備える。さらに、この固体メモリシステム中にデータを記憶するための方法を提供する。この方法は次のステップを含む。メモリ制御部が書込みコマンドを受け取る。この書込みコマンドに応答して、書込みデータが揮発性メモリ中に記憶される。データ転送要求に応答して、揮発性メモリから不揮発性メモリにデータが転送される。

(もっと読む)

チャージポンプにおいて電流をクランプする回路

【課題】

チャージポンプにおいて電流をクランプする回路が開示される。

【解決手段】

チャージポンプは、複数のスイッチング回路トランジスタを有するスイッチング回路を備える。同回路における第1及び第2の対のトランジスタの各々は、スイッチング回路トランジスタの内の対応する1つからの電流に対して、電流におけるスパイクが、同スイッチング回路トランジスタとチャージポンプのキャパシタとの間を通る経路を通って部分的にだけ伝送されるように、そのトランジスタがオフに切り替わっている間に追加経路を提供することができる。

(もっと読む)

分散型直列制御システム

【課題】外部の制御マネジャーのかわりに、あるいはこれに加えて、セル内に一体的に記憶させた制御論理によって各セルを制御できるようにし、かつセルを直列接続させてケーブル配線を少なくできるようにした、分散型トポロジーを提供する。

【解決手段】分散型検出、制御、通信を可能にするネットワークトポロジーにより、電源と、少なくとも2つの電導体を具備する通信チャンネルを介して電源ならびに相互がつながれる、複数のラインパワード直列インテリジェントセル(PSIC)と、各PSICに固有に参照符をつけるためのアドレス手段と、前記PSICのひとつに埋設したもしくは供給される制御論理にしたがって作動するためにPSICのひとつに結合された、少なくとも一つのペイロード素子と、を具備する。

(もっと読む)

不揮発性メモリのデイジーチェイン配置

【課題】組み込みフラッシュメモリおよび他のデバイスに関連した短所のいくつかを克服するメモリシステムを提供する。

【解決手段】フラッシュメモリシステムは、システム・イン・パッケージ(SIP)容器310の中に実装されている。前記システムは、フラッシュメモリコントローラ320と複数のフラッシュメモリデバイス330a〜330nとを有する。単一パッケージまたはモジュールに適用されるSIPは、多数の集積回路(チップ)を有する。フラッシュメモリコントローラは、SIP内の複数のメモリデバイスと外部システムとをインタフェースするように構成されている。メモリデバイスは、デイジーチェインカスケード接続に構成されており、前記デイジーチェインカスケードを通じて転送されたコマンドを介してフラッシュメモリコントローラに制御される。

(もっと読む)

遅延ロックループ/フェーズロックループにおける移相処理

【課題】

本開示は遅延ロックループ(DLL)及びフェーズロックループ(PLL)における移相処理に関する。

【解決手段】

DLLまたはPLLにおけるチャージポンプは、出力ノードに並列に接続されたキャパシタを備える。一次電流スイッチング回路は、ソース電流でキャパシタを充電し、シンク電流でキャパシタを放電する。補助ソース回路は、大きさの範囲を有する正の位相生成電流をソースする。正の移相生成電流の大きさは、少なくとも1つのソース選択信号により決定される。補助シンク回路は、大きさの範囲を有する負の移相生成電流をソースする。前記負の移相生成電流の大きさは、少なくとも1つのシンク選択信号により決定される。

(もっと読む)

出力遅延調整によるシリアル接続のメモリシステム

【課題】クロックデューティサイクルを訂正し、出力遅延調整を実行するシステム及び方法が、スレーブデバイスとして動作するシリアル接続のデバイス用に提供される。

【解決手段】マスタデバイスは第1のスレーブデバイスにクロックを供給する。各スレーブデバイスは、クロックを順に次のスレーブデバイスに送る。最下位のスレーブデバイスは、クロックをマスタデバイスに戻す。マスタデバイスは、送出クロックと帰還クロックとを比較し、デューティサイクル訂正又は出力遅延調整が必要かどうかを判定する。必要ならば、マスタデバイスは、スレーブデバイスに対するコマンドを生成し、出力して、デューティサイクル又は出力遅延調整を実行する。スレーブデバイスはそれぞれ、デューティサイクル訂正又は出力遅延調整を実行する回路を有する。実装形態では、各スレーブデバイスはメモリデバイスであり、マスタデバイスはメモリコントローラである。

(もっと読む)

デイジーチェーンカスケードデバイス

【課題】デバイスをデイジーチェーンカスケード配列でシリアルに連結する。

【解決手段】デバイスはデイジーチェーンカスケード配列で連結され、第1デバイスの出力部は、データ、アドレス及びコマンド情報等の情報並びに制御信号を第2デバイスに第1デバイスから転送するように、デイジーチェーンカスケードの後方にある第2デバイスの入力部に連結されている。デイジーチェーンで連結されたデバイスは、シリアル入力部SIとシリアル出力部SOとを備える。情報がデバイスにSIを通じて入力され、該情報がデバイスからSOを通じて出力される。デイジーチェーンカスケードの前方のデバイスのSOは、デイジーチェーンカスケードの後方のデバイスのSIに連結されている。前方のデバイスにSIを通じて入力された情報は、該デバイスのSOを通じて出力される。該情報は次いで、後方のデバイスのSIに転送される。

(もっと読む)

スケーラブルメモリシステム

【課題】任意の個数のメモリデバイスをサポートできるメモリシステムアーキテクチャを提供する。

【解決手段】メモリシステムは直列接続された複数のメモリデバイスを有する。各メモリデバイスは、他のメモリデバイス及びメモリコントローラとの間用の直列入出力インターフェースを有し、メモリコントローラはビットストリームでコマンドを出し、ビットストリームはモジュラコマンドプロトコルに従う。コマンドはアドレス情報及びデバイスアドレスと共にオペレーションコードを含み、アドレッシングされたメモリデバイスだけがコマンドに作用する。データ出力ストローブ信号及びコマンド入力ストローブ信号がデータのタイプおよびデータの長さを識別するために、各出力データストリーム及び入力コマンドデータストリームと並列に供給される。モジュラコマンドプロトコルは性能改善のために各メモリデバイス内での同時動作のために使用される。

(もっと読む)

1 - 10 / 106

[ Back to top ]