チェバ ディー.エス.ピー.リミテッドにより出願された特許

1 - 10 / 10

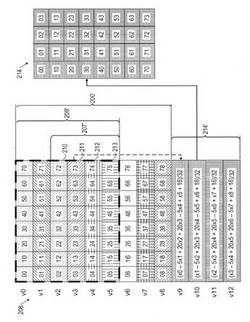

多次元データを転置することで垂直フィルタと水平フィルタを切替えるためのシステム、データ構造、および方法

【課題】多次元データたとえば画像データをフィルタリングするためのシステム。

【解決手段】プロセッサは、第1データ構造の単一行に水平方向に整列された多次元データ値を結合することで、水平フィルタを実行するための命令を受取ることができる。第2データ構造は、複数の個別アドレス指定可能内部メモリユニットを含んでよい。ロードユニットは、水平方向に整列された値を転置された配列でロードでき、個別アドレス指定可能メモリユニットにおける第2データ構造に、単一列内に垂直方向に整列された値として記憶する。単一列内の転置された各値は、個別アドレス指定可能メモリユニットのそれぞれ互いに異なる一つに別個に記憶され得る。プロセッサは、別個のメモリユニットに独立にアクセスすることで、水平フィルタによって結合用に指定された転置された各値を、独立に操作および結合できる。

(もっと読む)

多次元データをデータ競合なしで同時検索するための処理システム、データ構造およびデータ処理方法

【課題】多次元データをデータ競合なしで同時検索する。

【解決手段】1個のデータポートを有する単一の方形データアレイは、多次元ピクセルアレイを表すデータ要素セットを記憶できる。ロード/記憶ユニットはデータ要素セットを受取り、各別のアドレスポートを有する複数の個別アドレス指定可能データアレイの間で分割記憶できる。個別アドレス指定可能データアレイは、ピクセルアレイの多次元サブアレイを表すデータ要素サブセットからのデータ要素を記憶する単一行を含んでよい。1回の計算サイクルでデータ要素の完全なサブセットを検索するプロセッサは、個別アドレス指定可能データアレイのそれぞれに対応するそれぞれのアドレスポートにアクセスすることで、複数のアドレス指定可能データアレイそれぞれの単一行に同時アクセスできる。実行ユニットは、データ要素サブセットで命令実行できる。

(もっと読む)

動き推定処理における適応検索領域

【課題】ビデオコード化において動き推定中に既にコード化された基準画像の検索領域を動的に定義するシステムおよび方法を提供する。

【解決手段】複数のデジタル・データ・ブロックに分割される一連の画像を受け取ること、現在コード化中の画像の既にコード化されたデータブロック、たとえば、左データブロックおよび上部データブロックに関連する1つまたは複数の検索領域と、さらに現在コード化中のデータブロックと共通の位置にある基準画像の既にコード化されたデータブロックに関連する検索領域とに基づいて、既にコード化された基準画像内の検索領域を、現在コード化中の画像の現在コード化中のデータブロックに対して定義することを含む。

(もっと読む)

多次元映像データを処理するためのシステム、データ構造、および方法

【課題】多次元映像データを処理するためのシステム、データ構造、および方法を提供する。

【解決手段】多次元データを処理するためのシステム、プロセッサ、データ構造、および方法が提供される。第1の多次元データ配列の部分配列内において異なる次元に格納されている複数のデータ要素が互いに相関していると特定または判断される。異なる次元に存在する複数の相関データ要素は、第2のデータ配列の単一次元内にて順序付けられた位置にマッピングされる。単一次元に順番に格納された複数のデータ要素は、少なくともすべての相関データ要素が取得されるまで、各演算サイクルでデータ配列から反復的に取得される。その後、これらの相関データ要素が処理される。

(もっと読む)

コンピュータシステムにおいて割込みを処理するシステムおよび方法

【課題】パイプライン処理を行うプロセッサにおいて、割込み処理に関連する計算ペナルティを軽減する。

【解決手段】プロセッサパイプライン・スロットで一連の命令処理を開始する(600)。一連のスロットに続くプロセッサ・パイプライン・スロットで割込み処理を開始すると(610)、割込みサブルーチンが開始される時点で、連続命令が分岐命令を含み(620)、かつ、検出された分岐命令に関連する遅延スロットで割込みが処理されるときは(630)、検出された分岐命令を無効化し(640)、無効化された命令のアドレスをリターンレジスタに書き込み(650)、割込みサブルーチンから戻った後、リターンレジスタからの命令を実行する(670)。一方、連続命令が分岐命令を含まず(620)、あるいは、割込みが遅延スロットを占有しないときは(630)、割込みペナルティなしで命令処理を完了する(660)。

(もっと読む)

分岐誤予測バッファを用いるためのシステム及び方法

【課題】条件分岐命令を実行するためのシステム及び方法を提供する。

【解決手段】システムは、プロセッサ1を有する装置100と、データメモリユニット2と、プログラムメモリユニット3と、プログラムキャッシュ10とを含む。プロセッサ1はプログラム制御ユニット8を備え、分岐誤予測バッファ(BMB)17は、分岐メカニズム14によって予測されなかった正しい命令を記憶する。

(もっと読む)

マルチMACアーキテクチャにおける低電力FIRフィルタ

【課題】性能を犠牲にせずに低電力を実現するためのマルチMACアーキテクチャを提供する。

【解決手段】本発明の実施形態は、チェーンの第1の乗加算器の出力結果をチェーンの第2の後続乗加算器への入力として供給することによって、2つ以上の乗加算器ユニット(210、220、230、240)の乗加算器チェーンの演算をスケジュールして、比較的低いワット損を可能にするシステムおよび方法を対象とする。

(もっと読む)

高速サブピクセル動き推定

【課題】動画エンコーディングにおける高速なサブピクセル動き推定用のシステムおよび方法を提供する。

【解決手段】複数の非線形構築面を生成することと、複数の構築面と実際のマッチング規準面の複数のサンプルポイントとに基づき、ソースフレームと参照フレームとの間のマッチング規準を表す推定マッチング規準面をリアルタイムで生成することと、推定マッチング規準面上で位置をリアルタイムで選択することとによって、ソースフレームと参照フレームとの間の最良マッチを提供することを含む。

(もっと読む)

サブタスクによって複雑なタスクを実行するためのシステムおよび方法

【課題】サブタスクによってタスクを実行するためのシステム、デバイス、および方法を提供する。

【解決手段】複数のサブタスクが実行用に選択され(410)、実行順序が決定される(415)。先行するサブタスクのプロローグ(435)と後続のタスクのエピローグ(430)とが実行される。同じプロローグおよびエピローグが複数のサブタスクの対に用いられてもよい。このプロローグおよびエピローグの実行によって、サブタスクの連続的な実行が可能となる。

(もっと読む)

実時間に適応した量子化制御方法および量子化制御システム

【課題】画像の主観的品質を高めるため、適応量子化制御の実時間解法を提供すること。

【解決手段】ビデオ圧縮量子化を制御するシステムと方法は、データブロック試料の輝度成分の対角周波数、前記試料の輝度強度、および前記データブロックの動きの活発さに基づき量子化スケールオフセットを発生させることと;第2量子化スケールを受信すべく量子化スケールオフセットを用いて第1量子化スケールを調整することと;第2量子化スケールを用いてデータブロックを量子化することとを備える。

(もっと読む)

1 - 10 / 10

[ Back to top ]