インテル・コーポレーションにより出願された特許

1,031 - 1,040 / 1,101

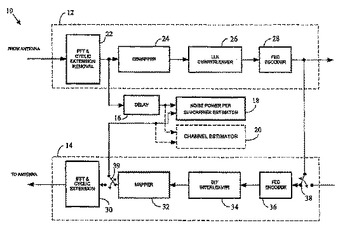

マルチキャリア・システムにおいてサブキャリア当たりの雑音電力を推定する方法と装置

まず受信マルチキャリア信号を復号することにより、マルチキャリア・システムにおけるサブキャリアに対する雑音電力が推定されるが、その際、その推定を行なうために復号信号情報および受信信号情報を使用する。ソフト決定またはハード決定復号が用いられてもよい。少なくともある実施例では、復号信号情報および受信信号情報を使用して、チャネル推定を行なうこともできる。  (もっと読む)

(もっと読む)

ネットワークベース管理におけるプロキシ、情報集約、及び仮想マシン情報の最適化のための方法、装置、及びシステム

方法、装置、及びシステムは、管理仮想マシンが、仮想マシンホスト上で他の複数の仮想マシンのためのプロキシとして動作することを可能にする。1つの実施形態において、管理仮想マシンは、ホスト上のそれぞれの仮想マシンに関連するネットワーク管理情報のデータベースを保持してもよい。ホスト上の高度な仮想マシンマネージャは、管理仮想マシンがホスト上の複数の仮想マシンに対する複数の管理メッセージを捕捉できるように、管理仮想マシンにインタフェースを提供してもよい。管理仮想マシンは、データベース内の情報に基づいて、複数のメッセージに応答してもよく、必要不可欠な情報を取得すべく、複数の仮想マシンにクエリーを発行してもよい。1つの実施形態において、管理仮想マシンは、ネットワーク管理メッセージに応答する前に、様々な仮想マシンからの情報を集約してもよい。 (もっと読む)

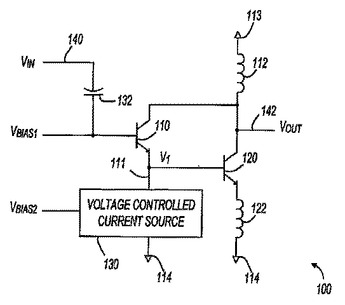

バイアスされたダーリントン・トランジスタ対、方法およびシステム

増幅器は、ダーリントン・トランジスタ対(110,120)および入力トランジスタ(110)中のバイアス電流を増加させるためのバイアスを与えるネットワークを含む。回路(100)は、入力トランジスタ(110)、第2トランジスタ(120)、無線周波数(RF)チョーク(112)、縮退インダクタ(122)、キャパシタ(132)および電圧制御電流源(130)を含む。入力トランジスタ(110)および第2トランジスタ(120)は、コレクタがノード(142)でともに結合され、入力トランジスタ(120)のエミッタがノード(111)に結合されて、ダーリントン・トランジスタ対を形成するために結合される。  (もっと読む)

(もっと読む)

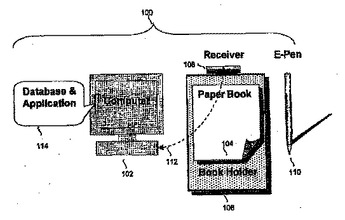

電子ペン−コンピュータのマルチメディアインタラクティブシステム

印刷物上の1つの選択されたオブジェクトを、1つのコンピュータシステムによって提供される1つの有効な応答と関連付けるためのシステムであって、印刷物上の位置を決定する1つのポインティングデバイスと、位置をコンピュータシステムに送信する1つの通信デバイスと、印刷物に関連する選択されたデジタルコンテンツに位置を関連付ける1つのプレーヤ要素であって、選択されたデジタルコンテンツはコンピュータシステムによってアクセス可能であり、位置及び関連付けられたコンテンツに少なくとも部分的に基づいて、1つの有効な応答をユーザに提供するプレーヤ要素とを備え、有効な応答は、オーディオコンテンツのレンダリング、ビデオコンテンツのレンダリング、イメージコンテンツのレンダリング、テキストコンテンツのレンダリング、及びコンピュータシステムによる1つのアクションの実行を含む。一実施形態において、ポインティングデバイスは、1つの電子ペンであり、印刷物は従来の紙の本である。

(もっと読む)

(もっと読む)

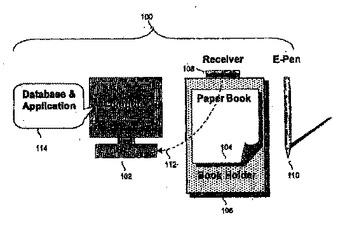

電子ペン−コンピュータのマルチメディアインタラクティブシステムのためのレスポンス生成

印刷物上の1つの選択されたオブジェクトを、1つのコンピュータシステムによって提供される1つの有効な応答と関連付けるためのシステムであって、印刷物の1つのページ上の1つのオブジェクトを定め、ページ上のオブジェクトの位置、ページのコンテンツ、及びコンピュータシステムによって実行されるべき、1つの関連する応答を関連づけるメーカ要素を備えるシステム。システムは、印刷物上の位置を決定する1つのポインティングデバイスと、位置をコンピュータシステムに送信する1つの通信デバイスと、印刷物に関連する選択されたデジタルコンテンツに位置を関連付ける1つのプレーヤ要素であって、選択されたデジタルコンテンツはコンピュータシステムによってアクセス可能であり、位置及び関連付けられたコンテンツに少なくとも部分的に基づいて、1つの有効な応答をユーザに提供するプレーヤ要素とを備え、有効な応答は、オーディオコンテンツのレンダリング、ビデオコンテンツのレンダリング、イメージコンテンツのレンダリング、テキストコンテンツのレンダリング、及びコンピュータシステムによる1つのアクションの実行を含む。

(もっと読む)

(もっと読む)

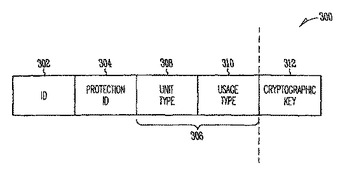

トラステッド・モバイル・プラットフォーム・アーキテクチャ

ある実施例において、装置は1以上の暗号化ユニットを具備する。本装置は、1以上のデータ暗号化キーと、この1以上のデータ暗号化キーに関連するヘッダを格納するためのメモリも具備する。関連ヘッダは、1以上の暗号化ユニットのうち、どのユニットがデータ暗号化キーを使用するかを定義する。  (もっと読む)

(もっと読む)

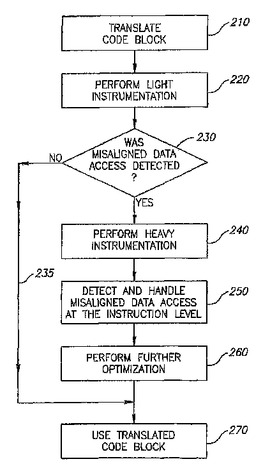

ミスアラインデータアクセスの検出及び処理のためのデバイス、システム、及び方法

ミスアラインデータアクセスの検出及び処理のためのデバイス、システム、及び方法。方法は、例えば、第1コンピューティングプラットフォームに適した第1フォーマットから第2コンピューティングプラットフォームに適した第2フォーマットに変換されたコードブロックの実行がもたらすミスアラインデータアクセスを検出する段階と、前記ミスアラインデータアクセスに従って前記コードブロックを修正する段階とを備える。

(もっと読む)

(もっと読む)

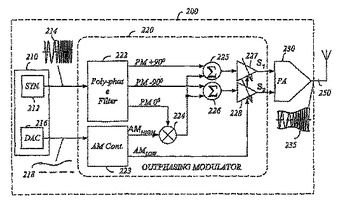

アウトフェイズ変調器

簡潔に述べると、少なくとも第1および第2アウトフェイズ信号を電力増幅器に提供するアウトフェイズ変調器を有する装置が示される。アウトフェイズ変調器は、電力増幅器の所要の出力電力レベルに基づいて、第1および第2制御信号の振幅レベルを変える振幅変調制御器によって、第1および第2アウトフェイズ信号の振幅を制御することができる。  (もっと読む)

(もっと読む)

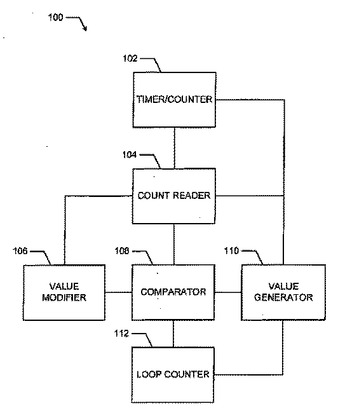

カウンタを用いて遅延を生成するための方法および装置

カウンタを用いて遅延時間を生成するための製造の複数の方法、装置、および複数の製品が開示される。特に、製造の前記複数の方法、装置、および複数の製品は、前記遅延時間に関連する複数のループの数の値およびカウンタに関連する少なくとも1つの特性値を決定する。残りのカウント値は、前記複数のループの数の値に基づいて、その後決定される。前記遅延時間は、前記カウンタと共に、前記複数のループの数の値および前記残りのカウント値に基づいて、生成される。

(もっと読む)

(もっと読む)

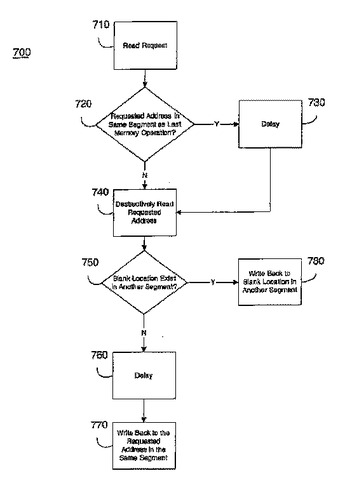

メモリ性能を改善する方法および装置

本発明の実施例に従ったメモリ性能を改善する装置および方法が提供される。本方法は、破壊読取り動作および書戻し動作を含む読取りサイクルを実行することを含むが、ここで、破壊読取り動作は、メモリの第1メモリ・セルから情報を読取ることを含み、また、書戻し動作は、第1メモリ・セルから読取られた情報をメモリの第2メモリ・セルに書き込むことを含む。  (もっと読む)

(もっと読む)

1,031 - 1,040 / 1,101

[ Back to top ]