インテル・コーポレーションにより出願された特許

1,041 - 1,050 / 1,101

パイプライン変換を通じて自動的にネットワークアプリケーションを並列化する装置及び方法

いくつかの実施形態において、パイプライン変換を通じてシーケンシャルネットワークアプリケーションを自動的に並列化する方法及び装置が記載される。一実施形態において、その方法は、ネットワークプロセッサをDステージプロセッサパイプラインに構成することを含む。構成されると、シーケンシャルネットワークアプリケーションプログラムは複数のDパイプラインステージに変換される。変換されると、DパイプラインステージはDステージプロセッサパイプライン内でパラレルに実行される。一実施形態において、シーケンシャルアプリケーションプログラムの変換は、シーケンシャルネットワークプログラムをフローネットワークモデルとしてモデリングし、複数の予備のパイプラインステージへとフローネットワークモデルから選択することによって実行される。他の複数の実施形態が記載及び請求される。

(もっと読む)

(もっと読む)

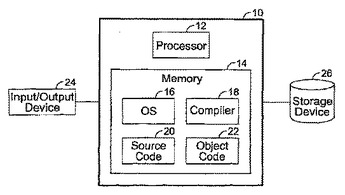

メモリアクセス命令のベクトル化

コンパイル方法は、最小データアクセス単位(MDAU)より小さい読み出し又は書き込みの複数のメモリアクセス命令を、複数の最小データアクセス単位を読み出す又は書き込む複数のメモリアクセス命令に変換する段階と、複数のメモリアクセス命令をベースアドレスにオフセットを加算する形式に変換する段階と、変換された複数のメモリアクセス命令の複数のサブセットを複数のパーティションにグループ化する段階と、複数の命令パターンとマッチする複数のサブセット内の複数の変換されたメモリアクセス命令をベクトル化する段階とを備える。

(もっと読む)

(もっと読む)

モジュラープラットホームシステム及び装置

モジュラープラットホームが用意される。モジュラープラットホームは、複数のモジュラープラットホームボードを受け入れるべく構成されたモジュラープラットホームシェルフと、モジュラープラットホームシェルフに結合されたデュアルプレナムとを含み、前記モジュラープラットホームは、他のモジュラープラットホームのデュアルプレナム又はスタンドアロンプレナムのプレナム部に結合されるべく構成される。

(もっと読む)

(もっと読む)

動的キャッシングエンジン命令

全般的には、1つの側面において、この開示は、少なくとも1つのプログラムの少なくとも一部の複数の命令を記憶する1つの命令記憶装置と、当該命令記憶装置に結合された複数のエンジンの組とを備える1つのプロセッサを示す。エンジンは、1つのエンジン命令キャッシュと、少なくとも1つのプログラムの少なくとも一部のサブセットを要求する回路とを有する。 (もっと読む)

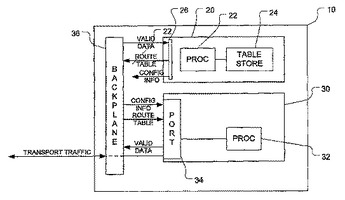

分散型外部ゲートウェイプロトコル

ボーダーゲートウェイ(10)は、コントロールカード(20)及び少なくとも1つのラインカード(30)を備える。コントロールカード(20)は、外部ゲートウェイプロトコルのコントロール部を実行するためのコントロールプロセッサ(22)及び複数の外部ゲートウェイルート及び複数の装置のルーティングテーブル(24)を有する。ラインカード(30)は、外部ゲートウェイプロトコルのオフロード部を実行するためのラインプロセッサ(32)及び少なくとも1つのコミュニケーションリンクの終端を可能にするコミュニケーションポート(34)を有する。バックプレーン(36)は、コントロールカード(20)及びラインカード(30)の交信を可能にする。

(もっと読む)

(もっと読む)

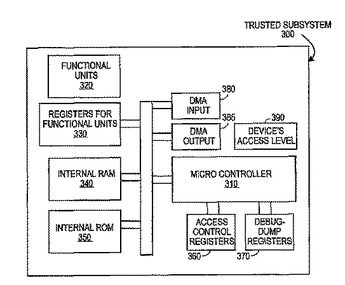

システム中の信頼されたコンポーネントのデバッグ

信頼されたサブシステム中の一実施例におけるデバッグ動作中に、

選択された領域へのアクセスをイネーブルおよびディセーブルにするために、かつ異なるエンティティによって相互に排他的にアクセスするために、パスワードが使用される。別の実施例では、プログラム可能なユニットは、どのアクセス領域がデバッグ動作のために選択されるかを定義するために使用される。  (もっと読む)

(もっと読む)

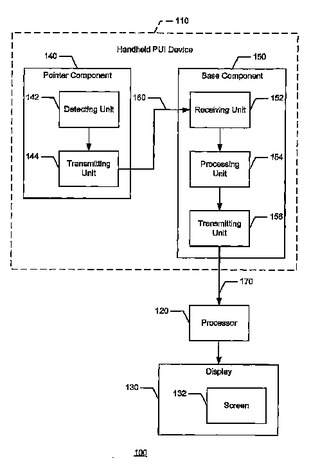

ハンドヘルドポインタベースユーザインターフェースを提供する方法及び装置

ハンドヘルドポインタベースユーザインターフェースを提供するための方法及び装置がここで述べられる。装置の1例は、ワイヤレスポインタコンポーネント及び1つ以上のベースコンポーネントを備える。ワイヤレスポインタコンポーネントは、ヒューマン−コンピュータインタラクション(HCI)イベントに関連する1つ以上のHCI信号を第一コミュニケーションリンク経由で送信する。1つ以上のベースコンポーネントは、第一コミュニケーションリンクを経由してワイヤレスポインタコンポーネントから1つ以上のHCI信号を受信するために、ディスプレイのスクリーンに機能的に結合される。さらに、1つ以上のベースコンポーネントは、1つ以上のHCI信号に基づいてワイヤレスポインタコンポーネントの動作情報及び位置情報の少なくとも1つを生成し、動作情報及び位置情報の少なくとも1つをディスプレイのスクリーン上のスクリーン情報を生成するように構成されたプロセッサへ第二コミュニケーションリンクを経由して送信するように構成される。

(もっと読む)

(もっと読む)

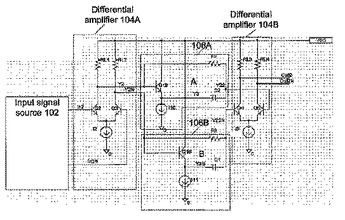

ドライブインピーダンスを低下させ、低減されたDCオフセットを提供する技術

簡潔には、最小コモンモード電圧の抑制で、低いRC時定数を有する複数の差動増幅器を結合する技術である。増幅器は入力信号源(102)、第1差動増幅器(104A)、第2差動増幅器(104B)、第1カップリングデバイス(106A)、第2カップリングデバイス(106B)を有する。入力信号源(102)は、第1差動増幅器(104a)に入力信号を供給する。

(もっと読む)

(もっと読む)

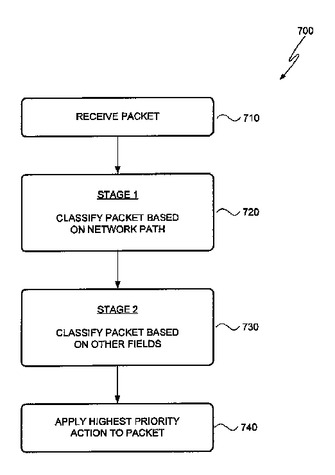

最適フィルタマッチング及びトランスポートレベル共有を用いた2ステージパケット分類のための方法及び装置

2ステージパケット分類のための方法及び装置であり、その2ステージパケット分類スキームは、第1ステージ及び第2ステージを有する。第1分類ステージでは、1つのパケットがパケットのネットワークパスに基づいて分類される。第2分類ステージでは、パケットは、パケットの1以上のトランスポート(又は他の)フィールドに基づいて分類される。最適フィルタマッチング及びトランスポートレベル共有の実施形態も開示され、これらの技術の1つ又は両方が2ステージ分類方法に実装される。

(もっと読む)

(もっと読む)

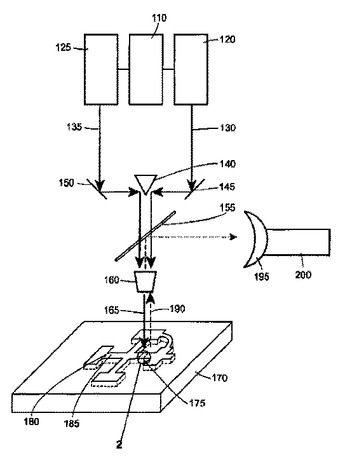

表面増感コヒーレント反ストークスラマン分光を用いた少数の分子を検出する方法および装置

【解決手段】ここで開示されているデバイスおよび方法は、表面増感コヒーレント反ストークスラマン分光法を用いて、核酸のような複数の被分析物を高分解能および高速応答時間で、検出する段階、同定する段階、および/または、定量化する段階に関する。本発明のある実施形態によれば、核酸のような被分析物210の少量の分子試料が、マイクロ流体チャネル、マイクロチャネル、またはナノチャネル185およびラマン活性な表面を含む試料セル175を通り、表面増感コヒーレント反ストークスラマン分光法(SECARS)により検出される。本発明の他の実施形態は、被分析物の検出の装置に関する。

(もっと読む)

(もっと読む)

1,041 - 1,050 / 1,101

[ Back to top ]