アドバンスト・マイクロ・ディバイシズ・インコーポレイテッドにより出願された特許

1 - 10 / 439

データバス反転信号伝達を用いる同時スイッチング出力の低減

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

仮想化処理システムにおけるアドレスマッピング

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

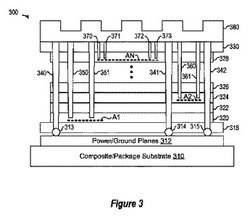

プロセス均一性及び熱消散を改善するダミーTSV(スルーシリコンビア)

【解決手段】

各々が能動回路領域を含むチップの積層体において、多重チップ積層体内の複数のスルーシリコンビア(TSV)開口をパターニングし、エッチングし、そして熱的伝導性材料で充填することによって、多重チップ積層体からの熱を熱的に伝導させるための複数のTSV構造が形成され、複数のTSV開口は、いずれの能動回路領域をも貫通せずに多重チップ積層体の実質的に全体を通って延びる第1の大きなTSV開口と、能動回路領域まで下に延びるが通過はしない第2の小さい開口と、を含む。

(もっと読む)

ガーベッジコレクションに対するCPUサポート

効率的なガーベッジコレクションのためのシステムおよび方法。汎用中央処理装置(CPU)は、世代別ガーベッジコレクション技法にしたがって、割り当てられたヒープを区分する。世代は、固定サイズカードに区分される。CPUは、アプリケーション実行中、直近のガーベッジコレクション以降の規定を満たしたダーティカードの表示をマーキングする。CPUが次のガーベッジコレクション開始条件が満たされたことを検出すると、CPUは、1つ以上のカードのルートアドレスの判定に対応する通知を特殊処理装置(SPU)へ送信し、各カードのルートアドレスは、前記マーキングされた表示のうちの1つに対応する。SPUは、単一命令複数データ(SIMD)並列アーキテクチャを有し、グラフィックス処理装置(GPU)であってもよい。SPUは、複数のカードルートアドレスを同時に演算するために、そのSIMDコアの並列アーキテクチャを利用することができる。次に、SPUは、ガーベッジコレクションアルゴリズムで使用されるこれらのアドレスをCPUへ送信する。 (もっと読む)

ハードウエアトランザクショナルメモリにおける自動サスペンド及び再開

【解決手段】

複数の処理コアによって共有されるメモリ(140)にアクセスすると共に複数のメモリアクセス動作をトランザクショナルモードで単一のアトミックトランザクションとして実行するように構成され且つプログラム制御転送等の暗黙サスペンド条件を決定することに応答してトランザクショナルモードをサスペンドするように構成されるコンピュータプロセッサ(102)のための装置及び方法が開示される。トランザクションを実行することの一部として、プロセッサは、投機的メモリアクセス動作によってアクセスされるデータを投機的データ(220)であるとしてマークする。サスペンド条件を決定すること(実行中のスレッドにおける制御転送を検出することによるものを含む)(230)に応答して、プロセッサはトランザクショナルモードの実行をサスペンドし、このことはサスペンドフラグ(240)をセットすることと投機的データ(250)のマーキングをサスペンドすることとを含む。後でプロセッサが再開条件(例えば制御転送からのリターンに対応するリターン制御転送)を検出した場合には、プロセッサは、投機的データのマーキングを再開するように構成される。

(もっと読む)

連続ウェルデカップリングコンデンサのためのシステムおよび方法

デカップリングコンデンサは、反対極性のウェル(102、104)内に形成された一対のMOSコンデンサ(106,108)を含む。各MOSコンデンサは、1組のウェル接続部および高ドーズ注入部(110、112、114、116)を有し、これにより、蓄積バイアスまたは空乏バイアス下における高周波性能が可能となる。各MOSコンデンサの上側導体は、他方MOSコンデンサのウェル接続部へと電気的に接続され、論理トランジスタウェルによって連続してバイアスされる。前記MOSコンデンサのウェル接続部および/または高ドーズ注入部は、ドーパント極性について非対称性を示す。 (もっと読む)

TLBサポート設計のIOMMU

【解決手段】

実施形態は、ページテーブルの構造及びフォーマットに依存しない改良されたトランスレーション挙動を有する入力/出力メモリ管理ユニット(IOMMU)のより小さくより単純なハードウエア実装を可能にする。実施形態はまた、デバイスに依存しない構造及び実装の方法を提供し、ソフトウエアのより大きな一般性を可能にする(より少ない特定のソフトウエアバージョンは同時に開発コストを低減する)。

(もっと読む)

ゲストローカル割込みコントローラを仮想化するように構成されたプロセッサ

一実施形態では、ハードウェア・プロセッサにおけるゲスト割込み制御ユニットは、仮想プロセッサに対応する記憶域に割込みが記録されていることを検出するように構成されてもよく、その割込みはその仮想プロセッサを対象とする。ハードウェア・プロセッサ上でアクティブである仮想プロセッサに応答して、ゲスト割込み制御ユニットは、その仮想プロセッサを含むゲストへの割込みを提供するように構成される。一実施形態では、プロセッサは、ゲストからの命令を実行するように構成され、そのプロセッサは、そのゲストにおける仮想プロセッサに関連付けられた割込みコントローラ状態データにアクセスする命令を検出するように構成され、かつ、そのプロセッサは、その命令に応答して仮想プロセッサに対応する割込みコントローラ状態データを格納する記憶域にアクセスするように構成される。 (もっと読む)

割込みの仮想化

一実施形態では、デバイス割込みマネージャは、ゲストに割り当てられたデバイスからの割込みを受信するように構成されてもよい。デバイス割込みマネージャは、ゲスト内の仮想プロセッサに対する割込みを記録するためにシステムメモリの中の記憶域を対象にした動作を送信するように構成されてもよく、割込みは対象となる仮想プロセッサに送達されることになる。一実施形態では、仮想マシン・マネージャは、現在実行中ではない仮想プロセッサに対するデバイス割込みマネージャによる割込みが記録されていることを検出するように構成されてもよい。仮想マシン・マネージャは、割込みに応答して、ハードウェア・プロセッサ上での実行のために仮想プロセッサをスケジュール設定するように構成されてもよく、又はスケジューリングのために仮想プロセッサに優先順位をつけてもよい。 (もっと読む)

プロセッサコアのハイパーバイザ離隔

プロセッサコアを利用するための技法は、オペレーティングシステムから独立的に使用するためにプロセッサコアを隔離することを含む。本発明の少なくとも1つの実施形態において、方法は、コンピュータシステムの複数のコアのうちの1つ以上のコアを含む、第1のサブセットのコア上でオペレーティングシステムを実行することを含む。オペレーティングシステムは、仮想マシンモニタの制御下でゲストとして実行する。本方法は、複数のコアのうちの1つ以上のコアを含む第2のサブセットのコア上でアプリケーションのための作業を実行することを含む。第1および第2のサブセットのコアは、相互に排他的であり、第2のサブセットのコアは、オペレーティングシステムに可視的ではない。少なくとも1つの実施形態において、本方法は、オペレーティングシステムから第2のサブセットのコアを隔離することを含む。 (もっと読む)

1 - 10 / 439

[ Back to top ]