エステーミクロエレクトロニクス ソシエテ アノニムにより出願された特許

1 - 10 / 31

マイクロプロセッサのモニタ回路により伝送されるメッセージの時間的相関

【課題】 マイクロプロセッサ(12)に集積化されるモニタ回路(18)の出力ターミナル(22)を介してデジタルデータメッセージを伝送する方法を提供する。そのメッセージは、マイクロプロセッサによる命令実行時に発生する決められたイベントを表す。本発明はまた、デジタルデータメッセージを伝送するための装置を提供する。

【解決手段】 方法は、特定のイベントに関連する少なくとも1つの特定のデジタルデータメッセージの伝送前又は伝送後に、特定のデジタルデータメッセージの識別子と、特定のデジタルデータメッセージの伝送に関連する命令及び先行のデジタルデータメッセージの伝送に関連する命令の間にマイクロプロセッサにより実行される命令の数のカウンタとを含む相関メッセージを伝送することから成るステップを有する。

(もっと読む)

シークレットキーを使った暗号化計算方法、及び、装置

【課題】SPA攻撃からDES暗号化法に保護するために、シークレットキー(K0)をマスクし、各アップデートされた導出計算キー(M’1、M’i)が、本方法の各実行時異なるようにする。

【解決手段】DES法の各ステップは、先立つキー計算ステップの間に、既知のキー計算方法に基づいて、以前に計算された導出キーから、アップデートされた導出キー(M’1、M’i)を算出する、複数キー計算ステップ(ET2)を有する。最初のアップデートされた導出キー(M’1)は、シークレットキー(K0)から取得されるものである。

(もっと読む)

安全化暗号化方法及び装置

【課題】暗号化法を実行して、コンポーネントの電力消費から又は電磁放射から、暗号化キーに関する情報を取得する物理的攻撃からコンポーネントを守る。

【解決手段】本発明は入力とシークレットキーから出力を得るために連続的に実行される計算のNサイクルを含むもので、入力をマスクし、計算サイクルにより使用され生成された各データをマスクするための第1マスキングレベルを生成するステップと、各計算サイクル内で操作されるデータをマスクするための第2マスキングレベルを生成するステップとからなる。

(もっと読む)

らせん形の閉じた磁気コア、及び前記閉じた磁気コアを備えた集積マイクロインダクタ

【課題】所与の全体的な寸法に対して、集積マイクロインダクタの磁気コアのコンパクト性を高め、かつ、インダクタンス値を増大させる。

【解決手段】閉じた磁気コア(1)は集積マイクロインダクタ用途に設計される。前記磁気コアはらせん形、好ましくは、略長方形のらせんを有する。このらせんは、クロージングセグメント(3)によって互いに結合される2つの端部(2)を備える。複数のブランチ(4,5)によって、前記磁気コア(1)を形成することができ、そして少なくとも2つのブランチを異なる平行な面に形成することができる。加えて、2つのブランチは異なる厚さとすることができる。前記磁気コアは空隙を備えることができる。

(もっと読む)

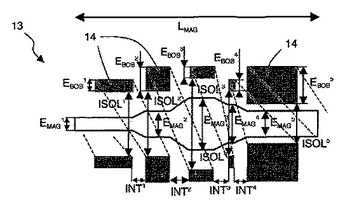

最適化されたソレノイド巻線

本発明による誘導マイクロデバイスは、複数の分離された長方形の折り返し部(14)を備え、直線的に伸びている、ソレノイド巻線(13)を備え、折り返し部の各々は、所定の寸法を有している。折り返し部(14)の寸法のうちの少なくとも1つは、可変であり、且つ、巻線(13)に沿った折り返し部の位置と、巻線(13)の所定の磁気特性(特に、均一な磁界及び/又は最適な品質ファクター)とに応じて、各折り返し部(14)について個別に決定される。折り返し部(14)の上記可変な寸法は、幅、長さ、厚さ(EBOB)、折り返し部の高さ(ISOL)、及び2つの隣接する折り返し部(14)間のギャップ(INT)の値から選択される。  (もっと読む)

(もっと読む)

いくつかのコイルブランチを有するコイル、及び当該コイルの一つを有するマイクロインダクタ

【課題】マイクロインダクタの性能を向上させ、同時にマイクロインダクタのコンパクト性を高める。

【解決手段】コイルは複数の非結合のターンを備え、各ターンは底面に長方形の平らな底部と、上面に長方形の平らな頂部と、2つの立上がり部と、を有する。ターンはコイルの包絡面のほとんど全てを満たし、最小隔離空隙が隣接するターンを分離する。同一のターンに対応する頂部と底部が、互いに関して揃えられ、かつ、対応する立上がり部の幅よりも大きな幅を持つ。ターンは複数の略平行なコイルブランチを構成し、2つの隣接するブランチの間に配置された、2つの隣接するブランチの立上がり部が単一の平面内に、交互に配置される。

(もっと読む)

圧電制御された集積磁性装置

【課題】圧電制御された集積磁性装置を提供すること

【解決手段】本発明に係る磁性装置(1)が基板の上に集積されており、本装置は、駆動電極(11a、11b)に結合され、圧電材料から作製された少なくとも1つの素子と、この圧電材料素子の応力下で変形可能な少なくとも1つの磁性素子(8)とを備える。本装置(1)は、基板に対して可動であるビーム(7)の形態を有し、基準長手軸(A1)に沿って所定の幅(W1)の2つの横断部(9)を備える。圧電材料素子は横断部(9)の少なくとも一部によって形成され、各横断部(9)は基板上に機械的に繋止するための領域を備える。横断部(9)は、磁性素子(8)が上に配置される、所定の幅(W2)の少なくとも1つの中心ブランチ(10)によって接続される。

(もっと読む)

異なる第1および第2の活性半導体領域を形成するための方法およびC−MOS構造を製造するためのその方法の使用

【課題】ハイブリッド基板の製造、特にC−MOS構造の製造を簡略化することを可能にする。

【解決手段】本発明の方法によれば、第1および第2の活性領域(1a,1b,1cおよび14a,14b)を支持体の前面上に形成することができ、前記活性領域はそれぞれ、互いに異なり且つ好ましくは同一の結晶構造を有する第1および第2の単結晶半導体材料によって形成されている。また、第1および第2の活性領域(1a,1b,1cおよび14a,14b)の前面は、同じ平面内にあるという利点を与える。そのような方法は、特に、多結晶および/またはアモルファス形態の第2の半導体材料から成るパターンおよび前記パターンと予め選択された第1の活性領域(1a,1b)との間の界面領域から単結晶形態で第2の半導体材料を結晶化させるステップにより第2の活性領域(14a,14b)を形成することから成る。また、支持体は、基板(4)と電気絶縁薄層(3)との積層によって形成され、電気絶縁薄層(3)の前面が支持体の前面を形成している。

(もっと読む)

可変キャパシタを形成する方法

【課題】望ましい形状を示す空洞に配置される導電層を含む可変キャパシタを製造する方法を提供する。

【解決手段】空洞の内部を覆う導電帯片、及び空洞の上に配置される弾力性のある導電膜を含む可変キャパシタを形成する方法であり、その空洞は、基板に凹所を形成する;その凹所に打ち延ばし可能な材料を配置する;打ち延ばし可能な材料の上方部に望ましい形状を与えるために、凹所のレベルで基板に型を載せる;その打ち延ばし可能な材料を硬化させる;及びその型を取り除くという工程により形成される。

(もっと読む)

ゲート電極に覆われたゲルマニウムベースのチャネルを有するトランジスタ及びその製造方法

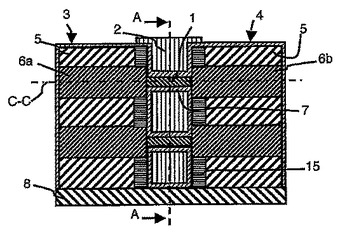

ソース電極(3)及びドレイン電極(4)はそれぞれゲルマニウム及びシリコン化合物からなる第1の層(5)と第2の層(6)を交互にすることで形成される。第1の層(5)は0%以上10%以下のゲルマニウム濃度を有し、第2の層(6)は10%以上50%以下のゲルマニウム濃度を有する。少なくとも1つのチャネル(1)はソース電極(3)及びドレイン電極(4)の各々の第2の層(6a、6b)を接続する。方法は、層(5,6)の積層体での狭領域で接続されたソース及びドレイン領域のエッチングを含む。そして、10%以上50%以下のゲルマニウム濃度を有するゲルマニウム及びシリコン化合物のシリコンを酸化し、ゲルマニウムGeを凝縮するために、前記積層体の表面熱酸化が行われる。狭領域の酸化シリコンは除去され、狭領域の凝縮されたゲルマニウム上にゲート誘電体(7)及びゲート(2)が堆積される。

(図2)  (もっと読む)

(もっと読む)

1 - 10 / 31

[ Back to top ]