アイメックにより出願された特許

21 - 30 / 302

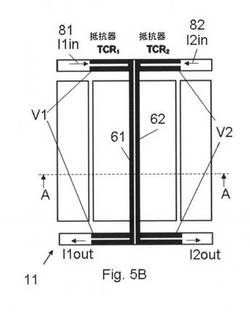

恒温制御されたMEMS発振器デバイス

【課題】低減した周波数ドリフトを達成することができる、実質的に安定した周波数で出力信号を発生するためのMEMSにシステムを提供する。

【解決手段】所定周波数は、温度依存性及び少なくとも一つの所定の特性に基づく。さらに、所定周波数で発振するためにMEMS発振器を励振するよう構成された励振機構、及び、抵抗感知を用いてMEMS発振器の温度を検出し、周波数ドリフトを最小限にするために温度依存性及び少なくとも一つの特性に基づいて、MEMS発振器の温度が所定温度の所定範囲内にあるか否かを決定し、MEMS発振器の温度を所定範囲内に留めるように適合させるように構成された温度制御ループを含む。さらに、MEMS発振器の所定周波数を出力するように構成された周波数出力を含んでいる。

(もっと読む)

ブリスターを伴わずにシリコン表面をパッシベーションする方法

【課題】シリコン表面に、Al2O3層を備えて表面パッシベーション層を形成するに際し、表面パッシベーション層は、パッシベーション層の良好な表面パッシベーション品質が維持されると共に、ブリスター形成が、高温でも回避される方法を提供する。

【解決手段】結晶シリコン基板の表面に表面パッシベーション層を形成する方法であって、この方法が、前記表面上に、15nm以下の厚さを有するAl2O3層を堆積するステップと、前記表面上への前記Al2O3層の堆積の後、500℃と900℃の間の範囲の温度でガス発生プロセスを行うステップと、ガス発生プロセスの後、前記Al2O3層上に、窒化シリコン層及び/又は酸化シリコン層等の少なくとも1個の追加誘電体層を堆積するステップとを備える。

(もっと読む)

ハイブリッドMOSFETデバイスの製造方法およびそれにより得られるハイブリッドMOSFET

【課題】第1および第2のチャネル材料をそれぞれ有する第1MOSFETと第2MOSFETを含むハイブリッドMOSFETデバイスの製造方法を提供する。

【解決手段】III−Vオン絶縁体スタックは、続いて第1基板に接続される第2基板の上に形成される。III−V層103および絶縁体層は第1領域から選択的に除去されて、これにより第1基板の半導体層が露出する。第1MOSFETの第1ゲートスタック109は第1領域の露出した半導体層上に形成される。第2MOSFETの第2ゲートスタック109’は第2領域のIII−V層の上に形成される。

(もっと読む)

一体型SERS測定のための導波路一体型プラズモン共鳴装置

【課題】表面増強ラマン散乱(SERS)セットアップと結びついた(一体型の)表面プラズモンポラリトン、及びそこでの導波路一体型共振器に使用可能である共振器構造を提供する。

【解決手段】共振器構造100は、2つの金属層110,130と、該2つの金属層110,130の間に挟持された絶縁層120とを有する金属−絶縁体−金属導波路を備える。共振器構造100はまた、絶縁層120内の少なくとも一部に配置され且つ絶縁層120内に共振キャビティの少なくとも1つのミラーを形成する、少なくとも1つのナノスケール金属反射体160a,160bを備える。

(もっと読む)

プラズマプローブ及びプラズマ診断のための方法

【課題】プラズマ反応器のチャンバ内におけるプラズマパラメータデータを測定する装置及び方法を提供する。

【解決手段】プラズマと接触する単一の平面ラングミュアプローブの表面でプラズマパラメータデータを測定すするために、プラズマと接触する単一の平面ラングミュアプローブ1の表面でバイアスコンデンサ2が単一の平面ラングミュアプローブ1とDCバイアス電源3との間で接続されている。続いて、DCバイアスが測定される結果として、バイアスコンデンサ2の放電電流が測定され、放電の間に単一のプローブでのプローブ電位が測定され、プローブ表面上の誘電体膜の存在及び/又は厚さを検出する。

(もっと読む)

半導体基板の洗浄方法および洗浄装置

【課題】容器中の液体を通る音波の行動により基板を洗浄し、容器中で実質的に音波の反射が発生しない方法に関する。洗浄効率に関して大きな改良を得る。

【解決手段】基板は、洗浄液を含むタンク中に、液体中で形成された音波に対して所定の角度で配置される。この角度は、伝達角度に対応し、即ち、基板表面から波が反射されない角度に対応する。減衰材料はタンク中に配置され、基板を通って伝達される全ての波を実質的に吸収するように配置される。

(もっと読む)

マイクロキャビティを封止するための方法

【課題】キャビティ、好ましくはMEMS又はNEMSデバイスが位置するキャビティを簡単な工程で封止するための方法を提供する。

【解決手段】薄膜層を犠牲層2上に堆積し、その後放出孔を薄膜層内でエッチングし放出工程を実施する。その際、少なくとも犠牲層の一部を放出孔を通じて除去し、キャビティを形成する。前記放出工程の前に狭窄層を放出孔の側壁に形成する。狭窄層を封止層5とする場合は封止層のリフローにより放出孔を閉鎖し、狭窄層が封止層でない場合には薄膜層上部に封止層を堆積し、直接封止層をリフローすることで放出孔を閉鎖する。

(もっと読む)

半導体デバイスおよび方法

【課題】光照射に適合した、少なくとも1つの電位障壁、又は表面障壁を持つ半導体デバイスの製造または処理に関し、高い絶縁破壊電圧と、大電流で低いキヤリア密度を有するデバイスの製造方法を提供する。

【解決手段】a)基板1を用意するステップと、b)第1エピタキシャル半導体層3を基板1の上に設けるステップと、c)1次元または2次元の繰り返しパターンを形成するステップと、を含み、パターンの各部分が、0.1〜50の範囲のアスペクト比を有するようにした方法を開示する。対応する半導体デバイス、電子回路および装置も開示している。

(もっと読む)

電子輸送チタン酸化物層

【課題】有機太陽電池に使用するのに十分な導電性を有し、ポスト処理を必要としない、溶液生まれのETL層に適した、チタン酸化物ゾルゲル層を形成するための、前駆体溶液形成方法を提供する。

【解決手段】以下の工程:a)酸を水と混ぜて、第1混合物を得る工程、b)第1混合物を水混和性アルコールと混ぜて、第2混合物を得る工程、c)一般式N(R1)(R2)(R3)の化合物を第2混合物と混ぜて、第3混合物を得る工程、d)例えば10分から15分のような、第3混合物が室温になるために十分な時間待つ工程、e)チタン酸化物前駆体を第3混合物に加えて、溶液を得る工程、を含むチタン酸化物ゾルゲル層を形成するための前駆体溶液形成方法。

(もっと読む)

太陽電池の製造方法

【課題】製造コスト下げると同時に良好なエネルギー変換効率を維持することにより、ワットピーク当たりのコストを削減した結晶シリコン太陽電池の製造方法を提供する。

【解決手段】結晶シリコン太陽電池の製造方法であって、第1ドーパント型の結晶シリコン基板を提供する工程と、注入工程を行い、これにより、結晶シリコン基板の表側に、第1型とは反対の第2型のドーパントを導入する工程と、注入工程後に、基板の表面上に水素含有層を堆積する工程と、水素含有層の堆積後に、熱処理を行い、これにより第2型のドーパントを電気的に活性化する工程とを含む。

(もっと読む)

21 - 30 / 302

[ Back to top ]